Contents lists available at ScienceDirect

Science of Computer Programming

www.elsevier.com/locate/scico

# Formal verification of function blocks applied to IEC 61131-3

# Linna Pang\*, Chen-Wei Wang, Mark Lawford, Alan Wassyng

McMaster Centre for Software Certification, McMaster University, 1280 Main St. W, Hamilton, Ontario, L8S 4K1 Canada

# ARTICLE INFO

Article history: Received 1 May 2014 Received in revised form 3 October 2015 Accepted 5 October 2015 Available online 19 October 2015

Keywords: Critical systems Formal verification Function blocks Tabular expressions IEC 61131-3

# ABSTRACT

Many industrial control systems use programmable logic controllers (PLCs) since they provide a highly reliable, off-the-shelf hardware platform. On the programming side, function blocks (FBs) are reusable components provided by the PLC supplier that can be combined to implement the required system behaviour. A higher quality system may be realized if the FBs are pre-certified to be compliant with an international standard such as IEC 61131-3. We present an approach: 1) to create complete and unambiguous FB requirements using tabular expressions; and 2) to verify the consistency and correctness of FB implementations in the PVS proof environment. We apply our approach to the examples in the informative Appendix F of the IEC 61131-3 standard. We examined the entire library of FBs and their supplied implementations described in structured text (ST) and function block diagrams (FBDs). Our approach identified issues in the informative examples, including: a) ambiguous behavioural descriptions; b) missing assumptions; and c) inconsistent implementations. We also proposed solutions to these issues.

© 2015 Elsevier B.V. All rights reserved.

# 1. Introduction

Many industrial control systems have replaced traditional analog equipment by components that are based upon programmable logic controllers (PLCs) to address increasing market demands for high quality [1]. Function blocks (FBs) are basic design units that implement the behaviour of a PLC, where each FB is a reusable component for building new, more sophisticated components or systems. Standards such as DO-178C [2] (in the aviation domain) and IEEE 7-4.3.2 [3] (in the nuclear domain) list acceptance criteria for mission- or safety-critical systems that practitioners need to comply with. Two important criteria are: 1) the system requirements are precise and complete; and 2) the system implementation exhibits behaviour that conforms to these requirements. In one of its supplements, DO-178C advocates the use of formal methods to construct, develop, and reason about the mathematical models of system behaviours. To this end, we present methods that support the use of formal notations for specifying the required behaviour of FBs, and for verifying that each FB (including composed FBs) complies with its requirements.

Tabular expressions [4,5] (a.k.a., function tables or tables) have proven to be both practical and effective in formally documenting system requirements in industry [6,7]. PVS [8] is a general purpose theorem prover that provides an integrated environment with mechanized support for writing specifications using tabular expressions and (higher-order) predicates, and for (interactively) proving that implementations satisfy the tabular requirements using sequent-style deductions. In

\* Corresponding author.

*E-mail addresses:* pangl@mcmaster.ca (L. Pang), wangcw@mcmaster.ca (C.-W. Wang), lawford@mcmaster.ca (M. Lawford), wassyng@mcmaster.ca (A. Wassyng).

http://dx.doi.org/10.1016/j.scico.2015.10.005 0167-6423/© 2015 Elsevier B.V. All rights reserved.

CrossMark

this paper we report on using tabular expressions to formalize the requirements of FBs and on using PVS to verify their correctness (with respect to tabular requirements).

As a case study, we attempted to verify the FBs<sup>1</sup> listed in "Informative" Annex F of the 2003 version of IEC 61131-3 [9] as well as the FBs described in the standard itself. IEC 61131-3 is an important standard with over 20 years of use on critical systems running on PLCs. We had two reasons for choosing IEC 61131-3 for our case study. First of all, this provided a number of FBs that represent useful behaviours in a number of application domains, so our methods could be applied to FBs that we knew were representative of industrial use. Secondly, although the FBs of Annex F are not technically part of the standard as indicated by the labelled "Informative", the entire document, including all annexes, has become the *de facto* standard for FBs. PLC vendors have based their libraries on the FBs from Annex F, as well as those described in the body of the standard.

The standard itself does not make any claim as to the completeness and appropriateness of the behaviour of FBs. In addition, no one has published a "validated and verified" version of the FBs in the standard. Thus, companies that develop mission-critical or safety-critical systems using PLCs had to qualify the behaviour of their libraries based on IEC 61131-3 (including Annex F), at considerable cost. If practitioners can use pre-defined and pre-verified FBs, then this will help raise the quality of FB-based implementations in industry without the overhead that would be required if each practitioner had to perform the verification separately.

Currently, some of the design specifications in the standard (expressed in source code) are incorrect, in that they are not what is commonly expected in practice. We believe that formal requirements of the FB behaviour, such as those provided by tabular expressions, help tool vendors and users of FBs have the same interpretations of the expected system behaviours. Also, formal descriptions are amenable to mechanized support such as PVS to verify the conformance of candidate implementations to a high-level, input-output requirements. For the purpose of this paper, we focus on FBs that are described in the more commonly used languages of structured texts (STs) and function block diagrams (FBDs). Note that two versions of IEC 61131-3 are cited here. The earlier version [9] has been in use since 2003. Most of the work reported in this paper relates to this version.

As we will see, a number of issues were uncovered in the FBs in the standard and in its informative Annex F. Our intent in the proceeding discussion is to illustrate how our methodology raised questions about some of these FBs. It is not a direct criticism of the standard, since the original mandate of the standard did not include the presentation of a pre-validated and pre-verified FB library. In fact, the standard does not attempt to define the required behaviour of each FB at the semantic level that we would expect from a requirements specification. Instead it uses code. These source programs are operational descriptions, making it hard to identify unexpected behaviour, and they are thus at an inappropriate level of abstraction for specifying requirements. Consequently, we had to provide the high-level requirements specifications based on our experience and on what we deduced was the intended behaviour of the FB. Readers may not agree with our version of the required behaviour, but we did make an honest attempt to define the behaviour that would be consistent with industrial norms. In any case, our motivation here is to demonstrate our methods, not to criticize the standard. We hope that readers will be interested that the methodology highlighted potential problems with FBs that have been in use for many years, and that this type of methodology can help us improve the quality of FB-based designs. In 2013, a new version of the standard was issued [10], and this version did not include Annex F. Some of the FBs in the new version do still exhibit behaviour that we believe could be improved through use of this methodology.

#### Our approach and contributions

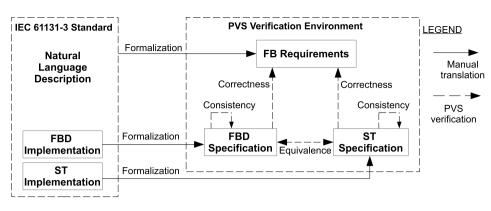

We now summarize our approach and contributions with reference to Fig. 1. As shown on the left of the figure, an FB will typically have a natural language description of the block behaviour accompanied by a detailed implementation in the ST or FBD description, or in some cases both. Based upon all of this information we created a black box tabular requirements specification in PVS for the behaviour of the FB (Section 3.2). The ST and FBD implementations are formalized as predicates in PVS, again making use of tables (Section 3.1). In the case when there are two implementations for an FB, one in an FBD and the other in ST, we attempt to prove their (functional) equivalence in PVS (Section 4.2). We also use PVS to attempt to prove the *consistency*<sup>2</sup> and *correctness* of each implementation with respect to its FB requirements (Section 4.1).

Using our approach, we identified a number of possible issues that warrant users' attention: ambiguous behaviour (Section 5.1); possible missing input assumptions (Section 5.2); and inconsistent implementations (Section 5.3). We compare our approach and results with other related work in Section 6, and end up with some concluding remarks in Section 7.

This paper extends [11] by including the following new contributions:

- We provide a complete example which illustrates the modelling of FB requirements in PVS (Section 3.2).

- A revised list of ST-to-PVS translation rules (Section 3.1.4) is included, sufficient to handle all the implementations included in IEC 61131-3 [9] and its Annex F. Constructs that are supported by the ST language but not used in Annex F of the standard [9] (e.g., CASE statement, WHILE and REPEAT loops, *etc.*) are not covered in our list of rules. Nonetheless,

<sup>&</sup>lt;sup>1</sup> PVS files are available at http://www.cas.mcmaster.ca/~lawford/papers/SCP2014. All formalization and proofs are conducted using PVS 6.0.

<sup>&</sup>lt;sup>2</sup> In this paper, we overload the term consistency in two contexts. Two implementations are *consistent* if they exhibit the same input-output behaviour. An implementation is *consistent* (or feasible) if for any legitimate input, it produces an expected output. However, the context should be clear when we use the term.

the value of our translation is justified by the fact that the Annex F example function blocks are commonly used in industry.

- We extend the discussion on the *SR* block by supplying the exact definitions of: 1) what we consider should be the black-box input-output requirements table; 2) its theory of consistency; and 3) its theory of correctness (Section 5.1.2).

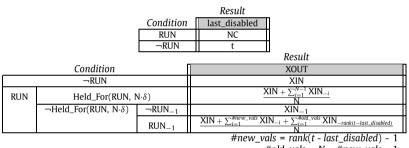

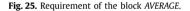

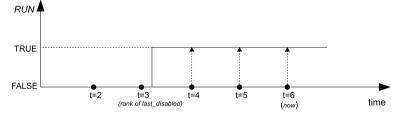

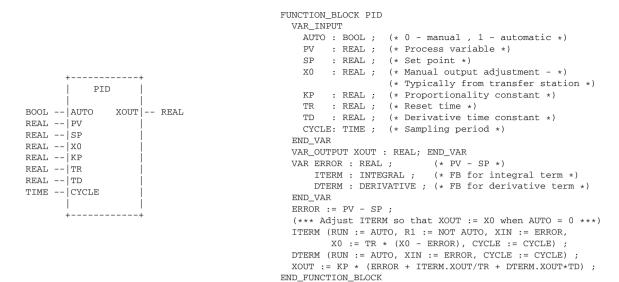

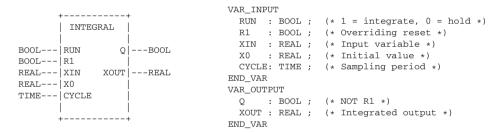

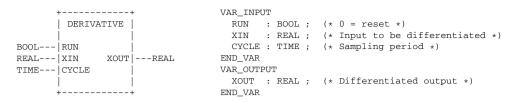

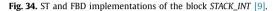

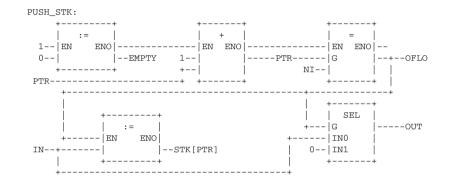

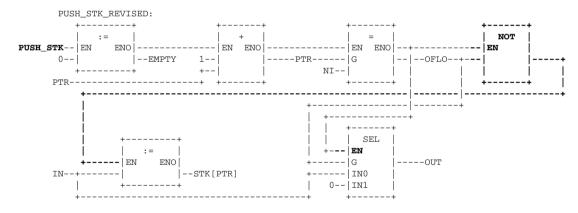

- We completed the verification of all FBs listed in IEC 61131-3 and found more blocks that warrant discussion: *HYS*-*TERESIS* (Section 5.2.2), *LIMITS\_ALARM* (Section 5.2.3), *DELAY* (Section 5.2.4), *AVERAGE* (Section 5.2.5), *PID* (Section 5.2.6), *DIFFEQ* (Section 5.2.7), and *STACK\_INT* (Section 5.3.1). We present tabular requirements for these blocks and propose solutions<sup>3</sup> for the potential issues we uncovered using this methodology.

In the next section we discuss background material: the IEC 61131-3 Standard, tabular expressions, and PVS.

# 2. Preliminaries

# 2.1. IEC 61131-3 standard for function blocks

Programmable logic controllers (PLCs) are digital computers that are widely utilized in real-time and embedded control systems. In an effort to unify the syntax and semantics of programming languages for PLCs, the International Electrotechnical Committee (IEC) first published IEC 61131-3 in 1993, and later revisions in 2003 [9] and 2013 [10]. Most of our research results were completed before the third edition was released.

We applied our methodology to the standard functions and also to the FBs listed in Annex F of IEC 61131-3 (2003). FBs are more flexible than standard functions in that they allow internal states, feedback paths, and time-dependent behaviours. We distinguish between *basic* and *composite* FBs: the former consist of standard functions only, while the latter can be constructed from standard functions and any other pre-developed basic or composite FBs.

Each FB is fed by input values, performs computations on them according to the behaviour specified in either ST or FBD (or both<sup>4</sup>), and produces output values. We focus on two programming languages that are covered in IEC 61131-3 for writing behavioural descriptions of FBs: STs and FBDs. These two languages are widely used in PLC-based control systems. The ST notation is a high level textural programming language which resembles another high-level programming language, Pascal. FBDs are a graphical programming notation. The fundamental concept behind FBDs is the inter-connections among block components, which specify the data flow dependency.

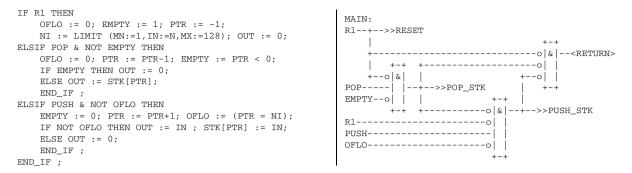

However, we found that in some cases for the same FB, its ST and FBD implementations (supplied in IEC 61131-3 2003 and its Annex F) cannot be mapped from one to the other, and thus cannot be proved to be equivalent; instead, we prove that one implementation conforms to the other (but not vice versa). For example, the FBD implementation supplied for *STACK\_INT* block (discussed in Section 5.3.1) has an explicit execution order for its component FBs, and such specificity is not required in the ST implementation for the same block.

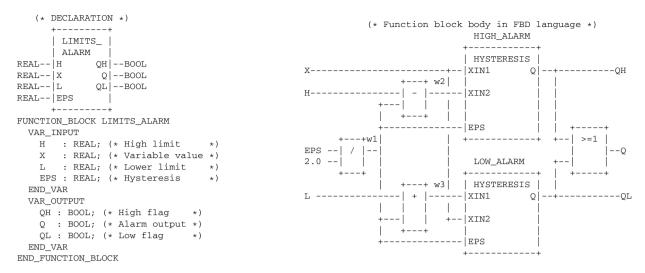

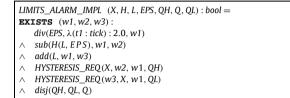

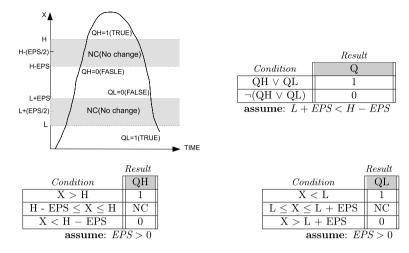

As an example of FBD implementation, we consider the *LIMITS\_ALARM* block (Annex F.6.7) that will be used as a running example for later sections. The FBD of the *LIMITS\_ALARM* block (Fig. 2) consists of two parts: 1) declaration of inputs and outputs; and 2) definition of the computation of its body. An alarm monitors the quantity of some input variable X, subject to a low limit L and a high limit H, with a hysteresis band of size *EPS*.

There are five component blocks of *LIMITS\_ALARM*: addition (+), subtraction (-), division (/), logical disjunction ( $\geq$  1), and two instances of hysteresis (i.e., *HIGH\_ALARM* and *LOW\_ALARM*). The internal connectives  $w_1$ ,  $w_2$  and  $w_3$  are used to

<sup>&</sup>lt;sup>3</sup> We deliberately choose the term *solution*, as opposed to *resolution*, in that we only propose possible solutions for the potential issues, and we do not intend to claim that they are the only solutions.

<sup>&</sup>lt;sup>4</sup> In the main text of the standard, each basic FB is defined in one single language. In the case of composite FBs, several languages can be used as the component FBs may be described using different programming languages.

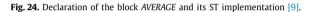

Fig. 2. Declaration of the block LIMITS\_ALARM and its FBD implementation [9].

|   |       |                                | Result           | _                                                            |

|---|-------|--------------------------------|------------------|--------------------------------------------------------------|

|   | Con   | dition                         | F                | $IF C_1$                                                     |

| 1 | $C_1$ | $C_{1,1}$                      | RES <sub>1</sub> | <b>IF</b> $C_{1.1}$ <b>THEN F</b> = $RES_1$                  |

|   | -     | C <sub>1.2</sub>               | RES <sub>2</sub> | <b>ELSEIF</b> $C_{1,2}$ <b>THEN</b> $F = RES_2$              |

|   |       |                                |                  |                                                              |

|   |       | <i>C</i> <sub>1.<i>m</i></sub> | RESm             | <b>ELSEIF</b> $C_{1,m}$ <b>THEN</b> $F = RES_m$              |

|   |       |                                |                  | <b>ELSEIF</b><br><b>ELSEIF</b> $C_n$ <b>THEN</b> $F = RES_n$ |

|   |       | Cn                             | RESn             |                                                              |

Fig. 3. Semantics of horizontal condition table (HCT).

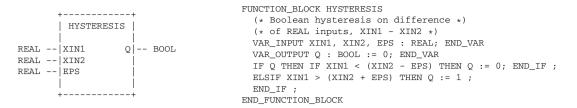

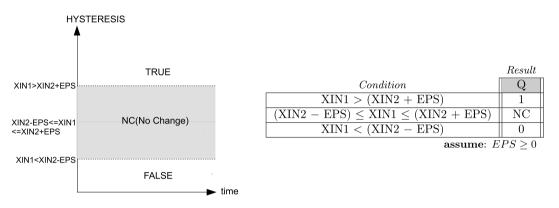

connect these internal blocks. The body definition visualizes how the ultimate and intermediate outputs are computed using two instances of the *HYSTERESIS* block. For example, the output *QL* is computed by manipulating the two output values *Q* from the top and bottom *HYSTERESIS* block:

LIMITS\_ALARM(H, X, L, EPS).Q =

HYSTERESIS(X,

$$H - \frac{EPS}{2.0}, \frac{EPS}{2.0}$$

).Q  $\lor$  HYSTERESIS( $L + \frac{EPS}{2.0}, X, \frac{EPS}{2.0}$ ).Q

where we write .Q to denote the output value resulting from the FB invocation in question.

**Roadmap for the running example.** We specify our interpretation of the precise input-output requirement of the *LIM-ITS\_ALARM* block using tabular expressions (Section 3.2). To verify its FBD implementation, we first formalize it in PVS (Section 3.1.5), then we verify its consistency and correctness (Section 4.1) with respect to the tabular requirement. Furthermore, we report any potential issues uncovered regarding this block (Section 5.2.3).

#### 2.2. Tabular expressions

Tabular expressions [12,13,4,5] are a proven and effective approach to describing conditionals and relations, and they are thus ideal for documenting many system requirements. They are arguably easier to comprehend and to maintain than conventional mathematical expressions. Reference [14] presents a relational semantics for tabular expressions which covers the most common types of tabular expressions used in software practice. Recently, reference [15] presented a new semantics for tabular expressions by using indexing to decouple the appearance of a tabular expression from its semantics. Tabular expressions have also been proven to be of great help both in inspections [7] and in testing and verification [16].

For our purpose of capturing the input-output requirements of function blocks in IEC 61131-3, tabular expressions of the form shown in Fig. 3 are appropriate. These tabular expressions are called *horizontal condition tables* (HCTs). The input domain is partitioned into condition rows in the left column(s), while rows in the right column(s), inside double borders, denote the corresponding output results. Rows in the input columns may be divided to specify sub-conditions. We may interpret the tabular structure in Fig. 3 as a list of "if-then-else" statements, without the sequence implications of the "if-then-else" construct. This is shown in the right part of the figure. Each row defines the input circumstances under which the output *F* is bound to a particular result value. For example, the first row corresponds to the predicate ( $C_1 \land C_{1.1} \Rightarrow F = RES_1$ ), and so on.

In documenting input-output behaviours using HCTs as illustrated in Fig. 3, we need to reason about their *completeness* and *disjointness*. Completeness ensures that there is an output specified for every combination of inputs – the rows cover

all input combinations, i.e., if we suppose that there are no sub-conditions,  $(C_1 \vee C_2 \vee \cdots \vee C_n \equiv TRUE)$ . Disjointness ensures that the rows do not overlap, e.g.,  $(i \neq j \Rightarrow \neg (C_i \land C_j), i, j \in \{1, 2, ..., n\})$ . Similar constraints apply to the sub-conditions, if any.

# 2.3. PVS language and prover

The Prototype Verification System (PVS) [8] was developed by the Computer Science Lab at SRI International as an interactive environment for writing specifications and conducting proofs. PVS consists of a specification language, predefined theories, a parser, a type checker, a theorem prover which supports several decision procedures, a symbolic model checker, pre-developed libraries, and utilities and documentation with examples in different application areas.

The PVS specification language is based on classical, typed higher-order logic. The base types include uninterpreted types and built-in types such as the Booleans. The type-constructors include functions, sets, tuples, records, enumerations, and inductively-defined (or coinductively-defined) abstract data types. In addition, users can adopt predicate subtypes and dependent types to introduce constraints to greatly increase the expressiveness and naturalness of specifications. But the expense is that these constrained types may generate proof obligations called *Type Correctness Conditions* (TCCs) during type-checking. In many cases, these generated TCCs can be discharged automatically by the theorem prover. PVS specifications are organized into theories that may include imported theorems, assumptions, definitions, axioms, lemmas, and goal theorems. Furthermore, the theories can be parameterized with constants, types, and theory instances. Definitions are conservative, e.g., subtype TCC generated with dependent types and termination TCC generated with recursive function definitions. PVS expressions support the arithmetic and logical operators, function application, lambda abstraction, and quantifiers, within a natural syntax. Tabular expressions are also provided with automated checks for disjointness and completeness. A prelude is included in PVS to provide over 1000 useful definitions and lemmas. The NASA PVS Library is also a collection of formal developments contributed and maintained by the NASA Langley Formal Methods Team [17].

The built-in theorem prover provides a collection of powerful proof commands to conduct propositional and quantifier rules, equality, and arithmetic formal reasoning under user guidance. Proof commands can be combined to form higher-level proof strategies. The PVS specification language is designed to work with the prover so that the inference mechanisms exploit the type information of a defined term and most of the generated TCCs are automatically discharged by the prover. To facilitate debugging of proofs, the PVS proof checker allows any proof step to be undone. It also permits modification of specification over the course of a proof. Proof scripts can be edited and rerun to support proof maintenance, allowing many similar theorems to be proved efficiently and adjusted economically.

We chose the PVS theorem prover to formalize the input-output requirements of function blocks primarily because it supports the syntax and semantics of tables (Section 2.3.1). In particular, for each table that is syntactically valid, PVS automatically generates its associated healthiness conditions of completeness and disjointness as TCCs. We have expertise built from past experience in applying PVS to check requirements and designs in the nuclear domain [6] that gave us confidence in using the toolset, and for modelling real-time behaviour we reused parts of the PVS theories from [18,19]. Our ongoing work on proving properties of real-time function blocks that consider timing tolerances also relies on the same set of theories. Nonetheless, the techniques presented in this paper are transferable to other theorem provers that support reasoning in higher-order logic, although checks of completeness and disjointness may then have to be manually encoded or a generator for the properties would have to be developed.

The function blocks in Annex F of IEC 61131-3 [9] involve only simple expressions using linear integer or real arithmetic and in our experience, when these constraints are provable, the table-related TCCs generated were typically automatically discharged by PVS's built-in default strategies. Alternatively, these table correctness conditions can be automatically discharged by an SMT solver, using the solver's theories for linear integer and real arithmetic. However, such verification may not be as convenient as in PVS, since one will need to manually encode these constraints for each table in the SMT solver, unless an existing tool that supports automated generation of correctness conditions (e.g., [20]) is chosen to create the tables. Further, when handling additional user-defined or library blocks that involve nonlinear arithmetic, the table's correctness conditions may be undecidable by an SMT solver. In this case, the PVS environment allows us to interactively prove these conditions.

# 2.3.1. Support for function tables in PVS

The PVS specification language provides two alternative built-in constructs for specifying function tables: *COND* and *TABLE*. They are semantically equivalent to a series of *IF*–*THEN*–*ELSE*–*ENDIF* statements. The use of *COND* and *TABLE* causes PVS to generate the proof obligations on disjointness and completeness to guarantee that the function table is well-defined. These can often be discharged automatically using the built-in proof strategies in PVS, i.e., (*COND*–*COVERAGE*–*TCC*) and (*COND*–*DISJOINT*–*TCC*). When the table cannot be automatically proved as well-defined, some useful feedback is returned. However, for readability, it is more advisable for users to adopt the *TABLE* construct, which will be translated into the equivalent *COND* construct in PVS for typechecking and proofs. Later in this paper (Section 5.2.2), we will discuss an issue in which the ST implementation supplied by IEC 61131-3 is formalized as a PVS table but the table fails the proof on the TCC of disjointness. The syntactic constructs that we use the most are *IF*–*THEN*–*ELSE*–*ENDIF* predicates and tables. An example of using tabular expressions to specify and verify the Darlington Nuclear Shutdown System (SDS) in PVS can be found in [6].

```

x: VAR int

f\_cond(x): bool =

COND x >= 0 \rightarrow TRUE,

x < 0 \rightarrow FALSE

ENDCOND

f\_table(x): bool =

TABLE | x >= 0 | TRUE ||

| x < 0 | FALSE ||

```

% Disjointness TCC generated (at line 15, column 2) for % COND x >= 0 -> TRUE, x < 0 -> FALSE ENDCOND % proved - complete f\_cond\_TCC1: OBLIGATION FORALL (x:int): NOT (x >= 0 AND x < 0); % Coverage TCC generated (at line 15, column 2) for % COND x >= 0 -> TRUE, x < 0 -> FALSE ENDCOND % proved - complete f\_cond\_TCC2: OBLIGATION FORALL (x:int): x >= 0 OR x < 0;</pre>

Fig. 4. Function tables and their TCCs in PVS.

| x: <b>VAR</b> real | <pre>% Subtype TCC generated (at line 108, column 17) for x % expected type nznum % unfinished</pre> |

|--------------------|------------------------------------------------------------------------------------------------------|

| g(x): real = $1/x$ | * UNLINISHED<br>$g_TCC1$ : <b>OBLIGATION FORALL</b> (x:real):x/=0;                                   |

Fig. 5. Expressions and well-definedness TCCs in PVS.

#### 2.3.2. Type correctness conditions

We briefly review failed TCCs that we encountered in our verification process. PVS automatically generates TCCs as proof obligations, which often can be automatically discharged, if they are provable, using the default proof strategies. However, in cases where they are too complicated to be discharged automatically, human interaction is required to guide the prover. Unproven TCCs often help users reveal issues (e.g., incompleteness, non-disjointness, ill-definedness, etc.) that can be traced back to the original specifications. One may choose to continue other proofs for the same specification while bypassing unproven TCCs, but until all TCCs have been discharged, a specification is not considered as type-correct, and lemmas and theorems that depend on theses unproven TCCs are considered provisional.

PVS checks the completeness and disjointness properties for a function table (Section 2.2) by automatically generating two types of TCCs: (*COND-COVERAGE-TCC*) for coverage (i.e., completeness) and (*COND-DISJOINT-TCC*) for disjointness. As an example, consider a simple Boolean function f(x) with an integer parameter x:

$f(x) = \begin{cases} TRUE & \text{if } x \ge 0\\ FALSE & \text{if } x < 0 \end{cases}$

In PVS, function f can be specified as a function table using either the COND construct or the TABLE construct as shown on the Left Hand Side (LHS) of Fig. 4. The associated TCCs<sup>5</sup> of (COND-COVERAGE-TCC) and (COND-DISJOINT-TCC) are automatically generated by PVS – see the Right Hand Side (RHS) of Fig. 4.

Since constraints can be imposed on the types in a PVS specification, subtype TCCs are generated for expressions whose types are defined using the predicate subtype notation (e.g., positive real numbers *posreal*). It makes very explicit and intuitive statements about the domains and ranges of functions, thereby contributing to the clarity of the PVS specification. The price paid is that it requires theorem proving to prove that expressions satisfy the constraints attached to types. Consider a general PVS function F, which is defined as:

$$F: \{x: T \mid P(x)\} \rightarrow \{y: T' \mid Q(y)\}$$

with the domain type constrained by predicate P and range type constrained by predicate Q. Whenever a function f is invoked, subtype TCCs are generated to ensure that, the output has to satisfy predicate constraint Q and the input has to satisfy predicate constraint P. Division is a particular instance of this problem.

As an example, consider a function g(x) with a real parameter x:

$$g(x) = 1/x$$

To model g in PVS, we use the built-in division operator (LHS in Fig. 5). For g to be well-defined, all expressions involved in its definition must be well-defined, i.e., the denominator x must be non-zero. Such a well-definedness constraint is formulated automatically by PVS as a TCC (RHS in Fig. 5).

There are other categories of TCCs that are automatically generated in PVS: existence TCCs and termination TCCs. Existence TCCs are generated for expressions whose types are declared as non-empty. Termination TCCs are generated to ensure that recursive functions always terminate for all possible inputs by requiring a well-founded *measure* to strictly decrease on each recursive calls. More precisely, recursive functions must be specified with a *measure*, that is a function whose signature

<sup>&</sup>lt;sup>5</sup> We show only the generated TCCs for function f\_COND, as the same TCCs are generated for f\_TABLE.

matches that of the recursive function, but with range type the domain of the order relation, which defaults to < on *nat* or *ordinal*.

# 2.3.3. Proofs in PVS

PVS has a powerful interactive proof checker to perform sequent-style deductions. The basic structure of the underlying calculus in PVS is a sequent [21]. Syntactically, a PVS sequent is showed as:

$$P_1, P_2, \ldots, P_m \vdash Q_1, Q_2, \ldots, Q_n$$

where  $P_i$ , i = 1, 2, ..., m are antecedent formulas,  $Q_j$ , j = 1, 2, ..., n are consequent formulas, and  $\vdash$  denotes entailment. Where the context is empty (i.e., no antecedent),  $\vdash$  may be dropped. The antecedents are combined by conjunctives while consequents are connected by disjunctives. Thus, the above PVS sequent is equivalent to the following expression in predicate logic<sup>6</sup>:

$P_1 \wedge P_2 \wedge \cdots \wedge P_m \vdash Q_1 \vee Q_2 \vee \cdots \vee Q_n$

The final goal of a PVS sequent is to determine whether at least one of its consequents is a logical consequence of its antecedents. In an editor panel of the PVS prover, a sequent is displayed as follows:

| {-1}     | P1 |

|----------|----|

| <br>{-m} |    |

| 1        |    |

|          |    |

| {n}      | Qn |

A sequent can be discharged only if one of the following three cases applies: 1) *FALSE* occurs in the antecedents; 2) *TRUE* occurs in the consequents; or 3) the formula *P* occurs in both the antecedents and the consequents [19]. A PVS sequent may be discharged by splitting it into sub-goals and by proving all of these sub-goals. The prover maintains a proof tree, and the final goal is to discharge each of its leaves by invoking relevant proof commands.

In practice, it is useful to decompose a complex problem into smaller ones, and to formulate and prove each of these subproblems as a lemma. For example, to verify the overall correctness of the *LIMITS\_ALARM* block (Section 4.1), we formulate the correctness conditions of its three output variables (i.e., *QL*, *Q*, and *QH*) as separate lemmas and conduct independent proofs.

Our justification for decomposing requirements by their outputs is two-fold. First, output variables in our proposed requirements tables do not depend upon each other. As discussed in Section 2.4, our requirements model describes idealized behaviour with an arbitrarily small clock-tick. At each discrete time instant, outputs are produced simultaneously as the inputs are updated. This means that the value of each output of a function block depends solely on those of the inputs. Second, all input-output requirements tables that we propose are completely functional. This claim is supported by the fact that all our proposed function tables are provably complete and disjoint, meaning that at any time instant, exactly one value can be produced for each output. Consequently, it is always possible to separate the definition of an output by projecting onto its relevant range of values. For example, consider any input types  $I_1$  and  $I_2$  and output types  $O_1$  and  $O_2$ , then we declare

$\begin{array}{l} \textit{REQ} \ : \ \textit{I}_1 \times \textit{I}_2 \rightarrow \textit{O}_1 \times \textit{O}_2 \\ \textit{req}_1 \ : \ \textit{I}_1 \times \textit{I}_2 \rightarrow \textit{O}_1 \\ \textit{req}_2 \ : \ \textit{I}_1 \times \textit{I}_2 \rightarrow \textit{O}_2 \end{array}$

where *REQ* represents the overall requirements function, and  $req_1$  and  $req_2$  represent, respectively, the requirements for the first output and second output, then for input values  $i_1 \in I_1$  and  $i_2 \in I_2$ , we have

$req_{1}(i_{1}, i_{2}) = \pi_{1} \circ REQ(i_{1}, i_{2})$  $req_{1}(i_{1}, i_{2}) = \pi_{2} \circ REQ(i_{1}, i_{2})$

where  $\pi_1$  and  $\pi_2$  are operators for, respectively, the first projection and second projection. This example can be generalized to arbitrary numbers of inputs and outputs.

Consequently, for each output, we are able to: 1) specify a separate function table that characterizes its relationship with the inputs; and 2) prove its correctness separately.

<sup>&</sup>lt;sup>6</sup> We use ¬, ∧, ∨, ⇒, ∀, and ∃ to denote, respectively, logical negation, conjunction, disjunction, implication, and universal and existential quantifiers. The corresponding notations in PVS are NOT, &, OR, IMPLIES, FORALL, and EXISTS.

# 2.4. Modelling time in PVS

As PLCs are widely used in real-time systems, the modelling of time is a critical aspect in our formalization. We consider a discrete-time model, where a time series consists of equally distributed time samplings, or "ticks". More precisely:

$\{t_0, t_1, t_2, \ldots, t_n, \ldots\} = \{0, \delta, 2\delta, \ldots, n\delta, \ldots\}$

where  $\delta \in \mathbb{R}^+$  is small enough to represent the time interval between two consecutive clock ticks. This kind of definition of *tick* is reproduced by [18] from [22]. It represents the type TIME in IEC 61131-3. In the real world, the sampling frequency is usually different from the clock tick frequency, i.e., the clock tick frequency should be significantly larger than the sampling frequency. In the software domain, all the actions occurring at the sampling times can be captured at the corresponding clock ticks. To approximate the continuous time model, the value of  $\delta$  may be arbitrarily small.

As a result, we define a *Time* theory in PVS:

```

delta_t : posreal

time : TYPE+ = nonneg_real

tick : TYPE = { t : time | EXISTS (n : nat) : t = n × delta_t }

```

The constant *delta\_t* is a positive real number. We define two type synonyms: *time* as the set of non-negative real numbers, and *tick* as the set of non-negative multiples of *delta\_t*. We will perform operations on *tick* [18]: e.g., *init* (the very first tick) and pre(t) (the tick preceding *t*, given that *init*(*t*) does not hold).

We define a characteristic predicate *init* which is *TRUE* only at the initial tick  $t_0$ :

init(t:tick):bool = (t = 0)

It is important to explicitly identify the initial values of internal or output variables of FBs in PLC-based control system. Given a time instant t, we use rank(t) to denote the ordinal of t in a discrete time setting.

$rank(t:tick):nat = t / delta_t$

For example, time instant 8.8 is the 4th tick given that  $delta_t = 2.2$ .

However, we choose to adopt the notion of real-valued ticks, rather than their corresponding integer ranks, for specifying function blocks (and their properties) as they more closely correspond to the sampling times in reality. In other words, the notion of ticks is more meaningful for the user to manipulate: e.g., for timer blocks, an output that denotes the elapsed time should be measured in real-valued units rather than integer ranks. However, given some fixed *delta\_t*, the set of real-valued ticks is isomorphic to its set of integer ranks. Consequently, proving lemmas or theorems in both domains is equally complex.

As PVS requires that all functions are total, to define the *pre* operator, we need a subtype *noninit\_elem* that denotes the set of ticks starting from  $t_1$  (i.e., excluding  $t_0$ ):

| noninit_elem : <b>TYPE</b> = | $= \{ t: tick \mid NOT init(t) \}$ |  |

|------------------------------|------------------------------------|--|

|------------------------------|------------------------------------|--|

Using *noninit\_elem*, the *pre* operator is defined as follows:

$pre(t:noninit\_elem):tick = t - delta\_t$

An important yet simple proposition we use in our model to prove some desired properties is an induction scheme over time ticks [19]. It states that a predicate *P* holds at all ticks if (a) *P* holds at the initial tick  $t_0$ ; and (b) for any t > 0, the fact that *P* holds at tick  $t_{n-1}$  implies that *P* holds at tick  $t_n$ . The formalization of this induction scheme is as follows:

```

\begin{array}{l} time\_induction: \ \textbf{PROPOSITION} \\ \textbf{FORALL} \ (P:pred[tick]): \\ (\textbf{FORALL} \ (t:tick):init(t) \Rightarrow P(t)) \ \land \ (\textbf{FORALL} \ (t:noninit\_elem): P(pre(t)) \Rightarrow P(t)) \\ \Rightarrow \ (\textbf{FORALL} \ (t:tick): P(t)) \end{array}

```

We consider most FBs listed in IEC 61131-3 as time-dependent. Each FB is formalized as a theory in PVS, parameterized by the constant time interval *delta\_t* and by importing our timing theory presented in this section.

# 3. Formalizing standard functions and function blocks using tabular expressions

We need to tailor our approach depending on the language(s) used to describe the required behaviour and the implemented behaviour of the FBs. In this case we have tailored our approach to deal with the languages used in IEC 61131-3. In many cases, IEC 61131-3 uses both ST and FBD to describe a single function block. However, both ST and FBD are informal, implementation-oriented notations, and they are thus not suitable for capturing a precise input-output relationship that is both complete and disjoint. Moreover, it is not possible to formally establish that these implementations are *correct* (i.e., consistent with the input-output requirement), since the required behaviour of the FBs in the standard and in Annex F is defined using natural language or not defined at all. We present a formal approach to define IEC 61131-3 standard functions and function blocks using tabular expressions and PVS. For each function block, we: 1) translate the supplied ST or FBD implementation into predicates in PVS (Section 3.1); and 2) capture its input-output requirement using tabular expressions in PVS (Section 3.2). Consequently, we have a unified, formal framework to verify the correctness of function blocks (Section 4).

# 3.1. Formalizing IEC 61131-3 function block implementations

We perform formalization at the level of standard functions, basic function blocks (FBs), and composite FBs. Similar to [23], we formulate each standard function or function block as a predicate, characterizing its input-output relation.

#### 3.1.1. Standard functions

IEC 61131-3 defines eight groups of standard functions, including: 1) data type conversion; 2) numerical; 3) arithmetic; 4) bit-string; 5) selection and comparison; 6) character string; 7) time and date types; and 8) enumerated data types. In general, we formalize the behaviour of a standard function f as a relation (i.e., Boolean function or predicate):

$$f(i_1, i_2, \ldots, i_m) : (o_1, o_2, \ldots, o_n) \triangleq R(i_1, i_2, \ldots, i_m, o_1, o_2, \ldots, o_n)$$

where the symbol  $\triangleq$  denotes that function f is formalized using relation (or predicate) R. Predicate R represents the specification of function f with input vector i and output vector o, by characterizing the precise relation on the m inputs and the n outputs of function f. Our formalization covers both timed and untimed behaviours of standard functions.

As an example, consider function *WEIGH* (Annex F.1), which takes as inputs a gross weight *gross\_weight* (a word encoding in Binary-Coded Decimal (BCD)) and a tare weight *tare\_weight* (an integer), and returns the net weight *net\_weight* (a BCD-encoded word). The standard supplies a one-line ST code program for the implementation of *WEIGHT* := INT\_TO\_BCD(BCD\_TO\_INT(gross\_weight) - tare\_weight), where INT\_TO\_BCD and BCD\_TO\_INT are standard conversion functions [9, p. 55]. We formalize the ST description of *WEIGH* in PVS by defining the output *net\_weight* as

# net\_weight = INT\_TO\_BCD( SUB( BCD\_TO\_INT(gross\_weight), tare\_weight ) ),

where *INT\_TO\_BCD* and *BCD\_TO\_INT* are PVS functions, whose names are deliberately chosen to match those in the standard, that formalize the corresponding conversions and *SUB* is the standard subtraction function. We use bit vectors supported by PVS to model words, and follow the standard rules of performing conversions between BCD-encoded words and integers. However, as our modelling is performed at the level of requirements, we do not consider implementation issues such as arithmetic overflows. Therefore, unless the input or output values are explicitly bounded like in the case of *WEIGH*, we use mathematical, unbounded integers or reals to model input and output values.

Nonetheless, as we stated earlier in the paper, since the focus of the standard is primarily on the notations used to describe the FB implementations, the standard does not include precise descriptions of the required behaviour of each FB. So as a demonstration of our approach, based on our experience and whatever we can deduce from the standard itself, we propose a formal requirements specification for the FB. More precisely, in the example above, we make the requirements of *WEIGH* and explicitly define the inputs domain. Of course, readers may disagree with our requirements specification and may have another in mind. This is quite usual in practice. The essential point here is that the requirements behaviour needs to be precise, and we did not make up these requirements behaviours simply to generate discrepancies between the requirements and implementations.

To complete this section we also discuss another standard function *ADD* (i.e., "+"). This function is stateless, and it may be used as an internal component of other FBs, such as *LIMITS\_ALARM* (see Fig. 2), which has the obvious formalization:  $ADD(IN_1, IN_2, OUT: int): bool = OUT = IN_1 + IN_2$ . Incorporating the output value *OUT* as part of the predicate parameters makes it possible to formalize basic FBs with internal states, or composite FBs. The predicate formalizing *ADD* can be reused to produce more complex composite FBs. For basic FBs with no internal states, we formalize them as function compositions of their internal blocks. As a result, we also support a version of *ADD* that returns an integer value:  $ADD(IN_1, IN_2: int):$  $int = IN_1 + IN_2$ . The functional formalization of *ADD* is used to discharge a consistency proof using instantiation, if an *ADD* block is one of the internal components.

|                 | ++            |

|-----------------|---------------|

| ++              | S1Q1          |

| SR              | 21   >=1   Õī |

| 1 1             | ++            |

| BOOL S1 Q1 BOOL | 1 1           |

| DOOT D          | R0  &         |

| BOOL K          | 01            |

| ++              |               |

|                 | ++ ++         |

| BOOL   R        | R0 &          |

Fig. 6. Declaration of the block SR and its FBD implementation [9].

# 3.1.2. Basic function blocks

A basic function block (FB) is an abstraction component that consists of standard functions. When all internal components of a basic FB are functions, and there are no intermediate values to be stored, we formalize the output as the result of a functional composition of the internal functions.

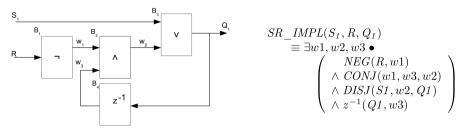

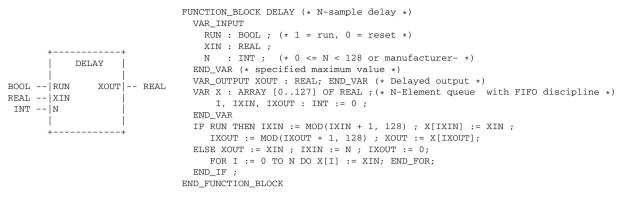

As an example in Fig. 6., consider the *SR* block, which implements a set-dominant latch (a.k.a., flip-flop). Block *SR* takes as inputs a Boolean set flag  $S_1$  and a Boolean reset flag R, and returns a Boolean output  $Q_1$ . The value of  $Q_1$  is fed back as another input of block *SR* itself. The value of  $Q_1$  remains *TRUE* as long as the set flag  $S_1$  is enabled.  $Q_1$  is reset to *FALSE* not only when the reset flag is enabled, but also when the set flag is disabled (so it cannot dominate the output result). Otherwise,  $Q_1$  stays unchanged. There should be a delay between the value of  $Q_1$  which is computed and passed to the next execution cycle. We formalize this by adding the explicit unit delay block  $z^{-1}$  and conjoining predicates for the internal blocks. The formalization of the delay block will be introduced in Section 5.1.2. IEC 61131-3 uses a circle (e.g., the upper input to conjunction block in Fig. 6) to negate the value of Boolean input signal. We explicitly replace such circle with a negation block wherever it occurs.

We formalize composite FBs in a similar manner.

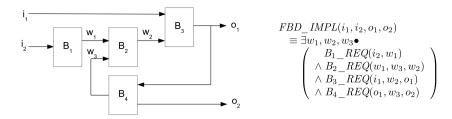

#### 3.1.3. Composite function blocks

Each composite FB contains as components standard functions, basic FBs, or other pre-developed composite FBs. For example, *LIMITS\_ALARM* (Fig. 2) is a composite FB consisting of standard functions and two instances of the pre-developed composite FB *HYSTERESIS*. Our formalization of each component as a predicate results in *compositionality*: a predicate that formalizes a composite FB is obtained by taking the conjunction of those that formalize its components. IEC 61131-3 uses ST or FBD, or both in the case that component FBs are described using different languages, to describe the behaviour of composite FBs. At this point we should note that predicates that formalize basic or composite FBs represent their black-box input-output relations. Since we use function tables in PVS to specify these predicates, their behaviours are deterministic. This allows us to easily compose their behaviours using logical conjunction. The conjunction of deterministic components is functionally deterministic.

# 3.1.4. Formalizing composite FB implementations: ST

As discussed in Section 2.1, in general it is not possible to translate an arbitrary ST implementation into its equivalent FBD implementation. Instead, for the purpose of our verification in PVS, we develop a limited set of translation rules that suffices to translate the ST implementations that are supplied by Annex F of IEC 61131-3 [9] into their equivalent expressions in PVS. This step of formalization in PVS allows us to verify the correctness of ST implementations against their input-output requirements (Section 3.2).

In this section, we discuss our ST-to-PVS translation in four phases: 1) state the challenge, scope of translation, and input assumptions; 2) provide an overview of translation; 3) provide a list of formal rules of translations; and 4) illustrate our translation rules via a number of examples.

# ST-to-PVS: challenge, scope of translation, and input assumptions

The main challenge of using PVS to formalize ST is that these two languages belong to two distinct paradigms. The ST programming language is an imperative notation, whereas the PVS specification language is a functional notation. For example, an IF-THEN-ELSE statement in ST is meant to perform conditional updates on the state (i.e., output or local variables), whereas an *IF-THEN-ELSE* expression in PVS is side-effect-free and returns a value (corresponding to the satisfying branch condition).

Nonetheless, our ultimate goal is to use *only* function blocks that are listed in the Annex of the standard [9] to illustrate our proposed approach. Consequently, our intention is not to formalize any arbitrary ST code whose syntax conforms with the standard. Instead, for the purpose of our verification, our rules of *ST-to-PVS* translation are designed to only handle the syntactic constructs of the ST language that are exploited in Annex F. That is, constructs that are supported by the ST language but not used in the Annex of the standard [9] (e.g., CASE statement, WHILE and REPEAT loops, etc.) Nonetheless, the value of our translation should be justified by the fact that the Annex F example function blocks are commonly used in industry. In other words, our translation rules should be able to handle many other similar function blocks outside the scope of Annex F [9].

For our *ST-to-PVS* translation, there are two primary assumptions about the input ST code. Both of the following assumptions are satisfied by all function blocks listed in Annex F [9].

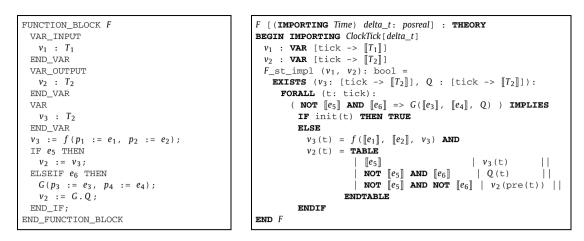

Fig. 7. ST-to-PVS translation: a contrived example.

- *Type correctness.* Each ST code is assumed to be type-correct: e.g., no references to unknown function blocks in variable declarations, no references to undeclared variables, no references to unknown formal parameters of a function in its invocation, etc. The PVS type system may be exploited to type-check the ST code, because if the source ST code is not type-correct, then neither will its corresponding formalized PVS theory. However, for the purpose of tracing type errors in the original code, if any, adopting a third-party ST programming tool is more appropriate.

- Single assignment. Each output or local variable in the body of the ST code gets assigned at most once. This will allow us to formalize each sequential composition operator (;) in ST as a logical conjunction ( $\land$ ) in PVS. As far as the formalization of function blocks in Annex F [9] is concerned, this assumption is always met. However, to relax this assumption, we will need to introduce a mechanism of building the dependency graph of variable assignments and, when it is acyclic, introduce auxiliary variables on the PVS side to impose the topological order.

Given the above assumptions, and the richness of the specification language and supported libraries of PVS, our *ST-to-PVS* translation is reasonably straightforward. Our translation rules shown below, although presented in a formal way, are still meant as guidance for users who want to translate the ST code manually into PVS. To adapt them for automation, some further context-sensitive analysis needs to be performed beforehand. Extension to the full coverage of ST syntax, or to the automation of these rules, is outside the scope of this paper.

# ST-to-PVS: an overview

Our strategy of translation is to map each complete ST program (i.e., with variable declarations and function block body) into a PVS theory. More precisely, we map (unconditional, conditional, or iterative) variable assignments into PVS predicates (Boolean functions) that encode the intended state effect as variable constraints. Let  $[-]: ST \rightarrow PVS$  denote our translation function that maps ST code to PVS expressions. Since we do not intend to handle the full ST syntax, the translation function is declared as partial.

An example translation Fig. 7 presents an overview of our *ST-to-PVS* translation. On the LHS of Fig. 7 we have the complete definition of a function block named *F*, declared with an input  $v_1$  (of type  $T_1$ ), an output  $v_2$  (of type  $T_2$ ). There is also a local variable  $v_3$  whose type is declared to match that of the output  $v_2$ . We assume that: 1) a standard function *f* is declared with parameters  $p_1$  and  $p_2$  and a return value of type  $T_2$ ; and 2) a function block *G* is declared with parameters  $p_3$  and  $p_4$  and an output value of type  $T_2$ ; 3) types of expressions  $e_1$ ,  $e_2$ ,  $e_3$ , and  $e_4$  match those of, respectively,  $p_1$ ,  $p_2$ ,  $p_3$ , and  $p_4$ ; and 4)  $e_5$  and  $e_6$  are Boolean expressions.

The body of function block *F* is defined as a sequential composition (denoted by a semicolon ;) of three programming statements: 1) assign to  $v_3$  the return value of invoking the standard function *f*; 2) invoke the function block *G*; and 3) assign to  $v_2$ , depending on the values of  $e_5$  and  $e_6$ . In both cases of invoking a standard function and a function block, the order in which argument values are passed is flexible: names of the formal parameters (e.g.,  $p_1$ ,  $p_2$ , etc.) are specify explicitly to bind those argument values. Moreover, there is a distinction between invocations of a standard function and of a function block: the former is an expression (a R-value), whereas the latter is a statement whose output must be retrieved in a later statement (e.g., G.Q).

On the RHS of Fig. 7 we have a PVS theory<sup>7</sup> *F* that formalizes the function block *F* defined on the LHS. As our translation is recursive, we write  $[T_1]$ ,  $[T_2]$ ,  $[e_1]$ ,  $[e_2]$ , etc. to denote the corresponding, equivalent PVS expressions. In the following, we summarize (part of) our translation strategy as exemplified in Fig. 7:

<sup>&</sup>lt;sup>7</sup> Note that negation (*NOT*) binds the tightest. Conjunction (*AND*) binds tighter than implication (*IMPLIES* or  $\Rightarrow$ ).

- For readability, we retain names of the function block and all its declared variables.

- The theory is always parameterized by an arbitrary clock tick interval *delta\_t*, which is used to instantiate the imported timing theory (Section 2.4).

- We formalize all ST (input, output, and local) variables as time-dependent logical variables in PVS (i.e., functions with the *tick* domain). However, we treat the parameter types of standard functions and function blocks differently in PVS. We formalize ST function blocks as input-output relations whose parameters are time-dependent (i.e., function blocks constrain inputs and outputs over time). On the other hand, parameters of standard functions are "untimed" (i.e., they are simple values instead of functions). All ST input and output variables are translated into global variables in PVS, so that they are implicitly universally quantified. On the other hand, local variables and return values from function invocations are translated into dummy variables of an existential quantification, so that they are hidden inside the function block.

- The function block body is formalized as a relation (i.e., Boolean function) which constrains the list of input and output variables over all discrete time ticks. The name of the relation has the \_st\_impl suffix to indicate that it is translated from some ST code.

- We define the input-output relation using a logical implication.

- The antecedent constrains output values of function block invocations, so that their output values can be referenced in the consequence. For each invocation that occurs in the context of some (nested) conditional branch, we guard it using an implication (e.g., the invocation of function block *G* is guarded by  $\neg [[e_5]] \land [[e_6]]]$ ). The guard (or the antecedent) may be used to prove that the input assumptions of the function block are satisfied upon its invocation. For example, in ST we may invoke the *HYSTERESIS* block under the condition *EPS* > 0, and we formalize it as the constraint *EPS* > 0  $\Rightarrow$  *HYSTERESIS*(...) in PVS.

- In the consequence, as output and local variables may be initialized, we use a universal quantification (over discrete *tick* values) to distinguish cases of the initial tick and non-initial ticks. At the initial tick, we constrain the values of those output and local variables that are explicitly initialized in the ST code; if no variables are explicitly initialized, the constraint is *TRUE*. At non-initial ticks, we constrain the value of each output variable according to how it is updated in the ST code. For example, the value of  $v_2$  at time t, where  $\neg init(t)$ , is equal to either: 1) the value of  $v_3$  at time t if  $[e_5]]$  holds; 2) the value of Q at time t if  $\neg [[e_5]] \land [[e_6]]]$  holds<sup>8</sup>; or 3) itself at the previous time tick if  $\neg [[e_5]] \land \neg [[e_6]]]$ .

# ST-to-PVS: formal rules of translation

In this section, we provide the list of translation rules that is sufficient for translating ST code supplied by Annex F [9] into PVS.

Notational convention For clarity, we typeset ST constructs in the code style (e.g., a + b), and PVS constructs in the math style (e.g., a + b). As our translation is recursive, when the translation of an ST construct (e.g., If-THEN-ELSE statement) involves the translation of its components (e.g., branching conditions, body statements, etc.), say *e*, then we write [e] to denote the translated PVS expression for *e*. Moreover, as partly illustrated in Fig. 7, we adopt the following conventions: 1) *e*,  $e_1$ ,  $e_2$ , etc., denote ST expressions; 2) *v*,  $v_1$ ,  $v_2$ , etc., denote ST variables; 3) *f*, *g*, *h*, etc. denote standard functions; 4) *F*, *G*, *H*, etc. denote function block names; 5) *T*,  $T_1$ ,  $T_2$ , etc. denote ST types; 6) *S*,  $S_1$ ,  $S_2$ , etc., denote ST statements; and 7) *i* denotes a loop counter.

*Translation context* Our translation function  $[\_]$  often needs to carry around context information from the translation of one component to another. First, since all ST variables are mapped into time-dependent variables in PVS, when generating a reference to a variable v, we need to determine either to refer to: 1) its entirety v as a timed sequence; 2) its value v(0) at the initial tick; or 3) its value v(t) at some non-initial tick t. Second, since for each output variable we need to infer its intended update as constraints, the current translation may need to know the target variable in order to make the corresponding inference. As a result, given that v is the target variable, and that  $t \in \{init, ninit, seq \}$  is the context for variable references, we write  $[\_]_v^t$  to denote the corresponding translation. We drop the context when it is not necessary for the translation in question to proceed. As an example, we write  $[\_]_v^{seq}$  for translating the invocation of a function block, where its arguments are expected to be time-dependent (i.e., timed sequences). In this example, the target variable is irrelevant and is thus dropped.

*Context-sensitive analysis* To assist our translation, we often need to extract information from the ST code fragment under consideration. For example, given a statement (e.g., the function block body as a sequential composition), we may extract the list of function block invocations that it makes. Furthermore, for those invocations, we need to extract the exact conditions where they occur and guard them accordingly (e.g., see Fig. 7 where the invocation of function block *G* is properly guarded). As another example, we may calculate the *write* set of a given statement (i.e., the set of variables that appear at the RHS

<sup>&</sup>lt;sup>8</sup> This branching condition is guaranteed by the fact that the ST IF-THEN-ELSE statement evaluates those conditions in order.

| Table 1    |          |       |             |

|------------|----------|-------|-------------|

| ST-to-PVS: | function | block | definition. |

| ST function block definition | PVS theory                                                                                                 | Delegates   |

|------------------------------|------------------------------------------------------------------------------------------------------------|-------------|

|                              |                                                                                                            | Table 2     |

| FUNCTION_BLOCK F             | F [( <b>IMPORTING</b> Time) delta_t: posreal] : <b>THEORY</b>                                              | Tables 7–6  |

| VAR_INPUT                    | <b>BEGIN IMPORTING</b> ClockTick [delta_t]                                                                 | Tables 8–10 |

| $v_1 : T_1$                  | $[\![v_1 : T_1]\!]$                                                                                        |             |

| END_VAR                      | $\begin{bmatrix} v_2 & \cdot & \overline{v_2} \end{bmatrix}$                                               |             |

| VAR_OUTPUT                   | $F_st_impl (v_1, v_2): bool =$                                                                             |             |

| $v_2$ : $T_2$                | <b>EXISTS</b> $([[v_3 : T_3]], [[Q : T_Q]]):$                                                              |             |

| END_VAR                      | $F\left(\llbracket e_1 \rrbracket^{seq}, \ldots, \llbracket e_n \rrbracket^{seq}, Q\right)$ <b>IMPLIES</b> |             |

| VAR                          | FORALL (t: tick):                                                                                          |             |

| $v_3$ : $T_3$ := $e$         | <b>IF</b> init(t) <b>THEN</b> $v_3(0) = \llbracket e \rrbracket^{init}$                                    |             |

| END_VAR                      | ELSE                                                                                                       |             |

| <i>S</i> <sub>1</sub>        | $v_2(t) = [S_1]_{v_2}$ AND                                                                                 |             |

| END_FUNCTION_BLOCK           | $v_3(t) = [S_1]_{v_3}$                                                                                     |             |

|                              | ENDIF                                                                                                      |             |

|                              | end F                                                                                                      |             |

of assignments), so as to determine if a variable has already been written. Tasks of such kind are standard and we do not address them in detail.

**Translation rule: function block definition** Table 1 presents the translation rules for function block definitions. The definition of each function block consists of two parts: variable declarations and body definition (denoted as  $S_1$ ). Without loss of generality, we consider the case where the function block declares one variable from each of the categories (i.e., input, output, and local).

As illustrated in Fig. 7, each function block defined in ST is mapped into a PVS theory that has a matching name, and instantiates our timing theory (Section 2.4) with an arbitrarily small, positive clock tick interval *delta\_t*. We delegate the translation of each input or output declaration in ST to Table 2.

The ST function block body  $S_1$  is mapped into the PVS relation  $F\_st\_impl$  that constrains values of its parameters: the list of inputs and outputs. Inside the definition of this relation, we use an existential quantification to hide: 1) the list of local variables (i.e.,  $v_3$ ); and 2) return values from function invocations. For 2), we use Q (of type  $T_Q$ ) to denote the list of return values that are referenced in  $S_1$ , if any.

In the case of function block invocations, as discussed, we model each function block *F* as a relation (a Boolean function) on the lists of inputs  $(i_1, i_2, ..., i_n)$  and outputs (Q), and each input or output is time-dependent and thus modelled as a timed sequence. In the case where the computation of output values depends on those of local variables, as mentioned above, we translate the relevant local variables into dummy variables of the corresponding existential quantification (see Fig. 7). As a result, the translated argument values are expected to be timed sequences (i.e.,  $[e_1]^{seq}, ..., [e_n]^{seq}$ ). As illustrated in Fig. 7, we use matching names<sup>9</sup> to capture values of outputs, so that in the same scope of context, these output variables may be referenced to define the constraints at both initial and non-initial time ticks. In the case where an invocation occurs within some (nested) conditional branch, we need to add an antecedent accordingly to guard the invocation. Inferring the exact antecedent to guard each invocation is an example of the context-sensitive analysis mentioned above, and we omit its details here.

In the case of the initial time tick, we constrain values of variables according to their specified initial values, if specified.<sup>10</sup> For example,  $v_3$  is initialized with the value  $[\![e]\!]^{init}$ . In the case of non-initial ticks, each declared local or output variable will trigger the generation of a constraint that encodes its intended update. When there are multiple output variables, we combine all these constraints using logical conjunctions. For example, for output variable  $v_2$ , we generate its constraint of intended update via  $[\![S_1]\!]_{v_2}$  (see Tables 7–6). So when given an ST statement  $S_1$ , our translation function effectively "projects"  $S_1$  onto the target variable (e.g.,  $v_2$ ). The result of the projection is a list of "guarded values", where guards correspond to the branching conditions of the IF-THEN-ELSE statements in the source ST code. The resulting list of guarded values can then be straightforwardly encoded as a *TABLE* expression in PVS. For example, as already seen in Fig. 7, the projection onto output variable  $v_2$  results in three guarded values.

**Translation rule: variable declarations** Table 2 presents the translation rules for variable declarations, where we reuse all variable names in PVS. Our treatment of the declarations of input (declared under VAR\_INPUT ... END\_VAR), output (declared under VAR\_OUTPUT ... END\_VAR), and local variables (declared under VAR ... END\_VAR) are the same.

<sup>&</sup>lt;sup>9</sup> Where multiple function blocks (e.g., *FB*1 and *FB*2) have outputs with the same name (e.g., *Q*), we resolve the ambiguity by adding their names as prefixes (i.e., *FB*1\_*Q* and *FB*1\_*Q*).

<sup>&</sup>lt;sup>10</sup> We may choose to specify an initial value for some uninitialized variable, but this is beyond the scope of the translation.

| ST variable declaration                                          | PVS variable declaration           | Delegates |

|------------------------------------------------------------------|------------------------------------|-----------|

| Case without initialization<br>v : T<br>Case with initialization | $v : \mathbf{VAR} [tick -> [[T]]]$ | Table 3   |

| v : T := e                                                       | $v : \mathbf{VAR} [tick -> [[T]]]$ |           |

| Table 3    |        |

|------------|--------|

| ST-to-PVS: | types. |

| ST type           | PVS type                                                         | Delegates                    |

|-------------------|------------------------------------------------------------------|------------------------------|

| INT               | int                                                              | Tables 8–10                  |

| REAL              | real                                                             |                              |

| BOOL              | bool                                                             |                              |

| WORD              | bvec                                                             |                              |

| TIME              | tick                                                             |                              |

| F                 | F                                                                |                              |

| ARRAY[ e1 e2 ] OF | T ARRAY [ subrange ( $[e_1]$ ) <sup><i>init</i>,</sup> , $[e_2]$ | <sup>init</sup> ) -> [[T]] ] |

| Table 4    |       |             |

|------------|-------|-------------|

| ST-to-PVS: | basic | statements. |

Table 2

| ST statement                                                                                            | PVS expression                                                                                                                                          | Delegates   |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Assignments $v := e$                                                                                    | With context variable <i>v</i><br>[[e]] <sup>ninit</sup>                                                                                                | Tables 8-10 |

| $ \begin{array}{l} x \ := \ e \\ v \ [ \ e_1 \ ] \ := \ e_2 \\ x \ [ \ e_1 \ ] \ := \ e_2 \end{array} $ | $ \begin{array}{c} \bot \\ \nu(pre(t)) \text{ WITH } [ (\llbracket e_1 \rrbracket^{ninit}) := \llbracket e_2 \rrbracket^{ninit} ] \\ \bot \end{array} $ |             |

Since each ST variable is time-dependent in our execution context of function blocks, we parameterize the PVS type [[T]] (translated from the ST type *t*) by discrete time ticks (Section 2.4). At the level of variable declarations, the translation does not consider whether or not an initial value is specified in the source ST code. Instead, such information is considered at the higher level of function block definitions (Table 1), where the context *init* is passed for translating the specified initial value (i.e.,  $[[e]]^{init}$ ).

**Translation rule: types** Table 3 presents the translation rules for types supported by ST. We categorize these types into four kinds: 1) primitive types (integers, reals, Booleans); 2) built-in types (e.g., words, time, etc.); 3) user-defined function blocks (e.g., *F*); and 4) arrays.

For primitive types, we can easily find the direct corresponding types in PVS. For built-in types, we import relevant theories to support their operations (e.g., bit vectors *bvec* from the *bv* prelude library, *tick* in Section 2.4, etc.). For a function block F that is user-defined, we simply reuse its name, assuming that its full definition is translated into a PVS theory.

The only structured type that we need for the purpose of Annex F [9] is that of arrays, which is also directly supported in PVS. The *ARRAY* type in PVS is essentially a function with a contiguous subset of integers for the domain and a proper range type, but the associated TCCs, e.g., validity of indices, are automatically generated by the prover. The operator *subrange* is supported by PVS to denote an integer range with specified lower and upper bounds. Presumably,  $e_1$  and  $e_2$  should be integer expressions, which is guaranteed by our assumption of input type-correctness. As the size of an array does not change at runtime, values of  $e_1$  and  $e_2$  must be available initially. As a result, we write  $[e_1]^{init}$  and  $[e_2]^{init}$  to denote the translated values in PVS.

**Translation rule: statements** Tables 4–7 present the translation rules for statements in ST (with no returned values). We assume that the context variable is v, meaning that  $[\_]_v$  is applied to infer the guarded values for v. We partition ST statements into two categories: 1) simple statements, including variable assignments and function block invocations; and 2) program combinators, including sequential compositions, IF-THEN-ELSE conditionals, and loops. Since all statements (including assignments) appear in the context of non-initial ticks, all involved expressions are translated via the invocation of  $[\_]_n^{init}$  (e.g.,  $[e_1]_n^{init}$ ).

Table 4 presents the translation for variable assignments in ST. In both cases of assignments, we return a special value  $\perp$  when the assignment target does not match the context variable  $\nu$ . A match in the case of a simple variable assignment is then straightforward: just return the translated value of the assignment source (i.e.,  $[e_1]^{ninit}$ ). A match in the case of an array variable assignment returns an array that is identical to the original (i.e.,  $\nu(pre(t))$ ), except that the item at the specified index is updated. To specify this, we pass as arguments the translated values of array index (i.e.,  $[e_1]^{ninit}$ ) and assignment source (i.e.,  $[e_2]^{ninit}$ ) to the PVS function override operator *WITH*.

Table 5 presents the translation for the IF-THEN-ELSE conditional statement in ST. Indeed, the rule generalizes the case presented in Fig. 7, with a (possibly empty) list of *ELSIF* statements. If the context variable v is not written at all

| ST statement                                           | PVS expression                                                                                                                                                                                                                                                                                                                                                        | Side condition     |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| IF $e_0$ THEN $S_0$<br>ELSIF $e_1$ THEN $S_1$          | <b>TABLE</b>   $\llbracket e_0 \rrbracket^{ninit}$   $\llbracket S_0 \rrbracket^{ninit}_v$      <b>NOT</b> ( $\llbracket e_0 \rrbracket^{ninit}$ ) <b>AND</b> $\llbracket e_1 \rrbracket^{ninit}$   $\llbracket S_1 \rrbracket^{ninit}_v$                                                                                                                             | written (v)        |

| ELSIF $e_{n-1}$ THEN $S_{n-1}$<br>ELSE $S_n$<br>END_IF | $ \  \operatorname{NOT} \left( \bigwedge_{j=0}^{n-2} \llbracket e_j \rrbracket^{ninit} \right) \text{ and } \llbracket e_{n-1} \rrbracket^{ninit}   \llbracket S_{n-1} \rrbracket_{v}^{ninit}     \\   \operatorname{NOT} \left( \bigwedge_{j=0}^{n-1} \llbracket e_j \rrbracket^{ninit} \right)   \llbracket S_{n} \rrbracket_{v}^{ninit}     \\ \mathbb{ENDTABLE} $ |                    |

|                                                        |                                                                                                                                                                                                                                                                                                                                                                       | $\neg$ written (v) |

Table 5

ST-to-PVS: conditional statements.

¬written (v)

where written  $(v) \triangleq (\exists i \bullet v \in write (S_i))$

Table 6

ST-to-PVS: loop statements.

| ST statement                                  | PVS expression                                                                                                                                                                                                                                                                                                                                         | Side condition       |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| FOR $i := e_1$ TO $e_2$<br>DO<br>S<br>END_FOR | $\begin{aligned} &\textbf{for} [\llbracket T \rrbracket] (\llbracket e_1 \rrbracket^{ninit}, \llbracket e_2 \rrbracket^{ninit}, \nu(pre(t)), \\ & \textbf{LAMBDA}  (i: \textbf{subrange}(\llbracket e_1 \rrbracket^{ninit}, \llbracket e_2 \rrbracket^{ninit}), \nu: \llbracket T \rrbracket): \\ & \nu = \llbracket S \rrbracket_{\nu} \end{aligned}$ | $v \in write (S)$    |

|                                               | $\perp$                                                                                                                                                                                                                                                                                                                                                | $v \notin write (S)$ |

| Iddle /    |            |             |    |

|------------|------------|-------------|----|

| ST-to-PVS: | sequential | composition | n. |

T-1-1- 7

| ST statement                    | PVS expression    | Side condition                           |

|---------------------------------|-------------------|------------------------------------------|

| Sequential cor                  | nposition         |                                          |

| s <sub>1</sub> ; s <sub>2</sub> | $[[S_1]]_{v}$     | $\llbracket S_2 \rrbracket_{\nu} = \bot$ |

| s <sub>1</sub> ; s <sub>2</sub> | $[\![S_2]\!]_{v}$ | $\llbracket S_1 \rrbracket_{\nu} = \bot$ |

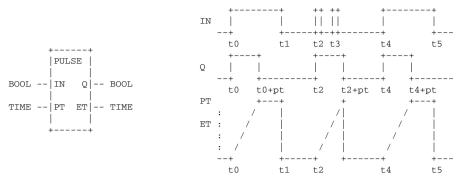

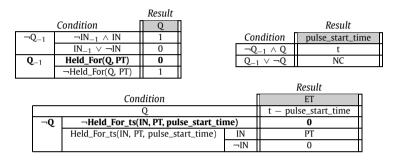

by any of the body statements  $S_i$  ( $0 \le i \le n$ ), then we return  $\bot$ . Otherwise, to correspond to the execution semantics of the ST IF-THEN-ELSE statement, each guard in PVS is defined as the conjunction of: 1) the translated value of the corresponding branching condition (e.g.,  $[e_1]^{ninit}$ ); and 2) translated values of all branching conditions that are checked before it (e.g.,  $[e_0]^{ninit}$ ). We use  $\bigwedge$  as a meta-operator to denote the conjunction of a sequence of expressions occurring in PVS.