## SAMPLED-DATA SUPERVISORY CONTROL

By Yu Wang, B.Eng

A Thesis Submitted to the School of Graduate Studies in partial fulfilment of the requirements for the degree of

Master of Applied Science Department of Computing and Software McMaster University

© Copyright by Yu Wang, January 15, 2009

ii

MASTER OF APPLIED SCIENCE(2006) (Software Engineering)

McMaster University Hamilton, Ontario

| TITLE:      | Sampled-data Supervisory Control    |

|-------------|-------------------------------------|

| AUTHOR:     | Yu Wang, B.Eng(McMaster University) |

| SUPERVISOR: | Dr. Ryan Leduc                      |

NUMBER OF PAGES: i, 390

## Abstract

This thesis focuses on issues related to implementing theoretical Discrete-Event Systems (DES) supervisors, and the concurrency and timing delay issues involved.

Sampled-data (SD) supervisory control deals with timed DES (TDES) systems where the supervisors will be implemented as SD controllers. An SD controller is driven by a periodic clock and sees the system as a series of inputs and outputs. On each clock edge (tick event), it samples its inputs, changes states, and updates its outputs.

In this thesis, we identify a set of existing TDES properties that will be useful to our work, but not sufficient. We extend the TDES controllability definition to a new definition, SD controllability, which captures several new properties that will be useful in dealing with concurrency issues, as well as make it easier to translate a TDES supervisor into an SD controller.

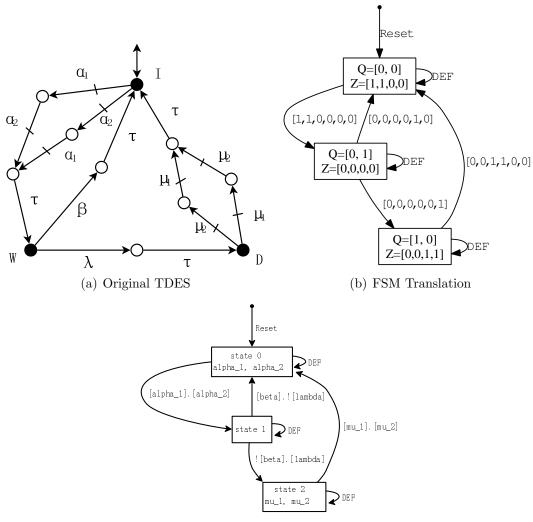

We then establish a formal representation of an SD controller as a Moore Finite State Machine (FSM), and describe how to translate a TDES supervisor to a FSM, as well as necessary properties to be able to do so. We discuss how to construct a single centralized controller, as well as a set of modular controllers and show that they will produce equivalent output.

Next, we capture the enablement and forcing action of a translated controller in the form of a TDES supervisory control map, and show that the closed-loop behavior of this map and the plant is the same as that of the plant and the original TDES supervisor. We also show that our method is robust with respect to nonblocking and certain variations in the actual behavior of our physical system.

We also introduce a set of predicate-based algorithms to verify the SD controllability property, as well as certain other conditions that we require. We have created a software tool for verifying these conditions and provide the source code in the appendix. We have implemented these algorithms using binary decision diagrams (BDD).

For illustrative purpose, we have produced a set of examples which fail the key conditions discussed in this thesis, as well as a successful application example based on a Flexible Manufacturing System. We also presented the corresponding FSM, iv

translated from the example's supervisors.

## Acknowledgment

I will definitely first give my thanks to my supervisor, Dr. Ryan Leduc, who I have been working for since I was an undergraduate. I would have never been able to accomplish this task without the great great amount time, constant guidance, and support he has given me. His expertise in the area of discrete event control systems is the most valuable source of help for the whole period of this work.

I'd also like to thank Raoguang Song for his preceding work on the BDD based symbolic verification tool for HISC. His code base saved me a lot of effort in understanding and starting the software implementation.

At last my thanks go to my beloved father Xuhong Wang, and mother Baoxiang Yun for their unlimited support and Wen Xie for her great understanding and confidence in me. This thesis is dedicated to them. vi

## Contents

| C             | ontei        | nts                                                                                                       | vii |  |

|---------------|--------------|-----------------------------------------------------------------------------------------------------------|-----|--|

| $\mathbf{Li}$ | st of        | Figures                                                                                                   | xi  |  |

| 1             | Introduction |                                                                                                           |     |  |

|               | 1.1          | Objective                                                                                                 | 4   |  |

|               | 1.2          | Related Work                                                                                              | 7   |  |

| <b>2</b>      | Dis          | crete-Event Systems Preliminaries                                                                         | 11  |  |

|               | 2.1          | Algebraic Preliminaries                                                                                   | 11  |  |

|               |              | 2.1.1 Strings                                                                                             | 11  |  |

|               |              | 2.1.2 Languages                                                                                           | 12  |  |

|               |              | 2.1.3 Nerode Equivalence Relation                                                                         | 12  |  |

|               | 2.2          | Discrete Event Systems                                                                                    | 13  |  |

|               |              | 2.2.1 Generator $\ldots$ | 13  |  |

|               |              | 2.2.2 Synchronization and Product DES                                                                     | 17  |  |

|               |              | 2.2.3 Controllability and Supervision                                                                     | 19  |  |

|               | 2.3          | Timed Discrete Event Systems                                                                              | 21  |  |

|               |              | 2.3.1 Basic Structure                                                                                     | 22  |  |

|               |              | 2.3.2 Controllability and Supervision                                                                     | 22  |  |

| 3             | San          | npled-Data Systems                                                                                        | 31  |  |

|               | 3.1          | Sampling Inputs                                                                                           | 33  |  |

|               | 3.2          | SD Controllable Languages                                                                                 | 37  |  |

|               | 3.3          | Future Work                                                                                               | 45  |  |

| 4             | Mo           | ore Synchronous Finite State Machines                                                                     | 47  |  |

|               | 4.1          | Formal Model                                                                                              | 48  |  |

|               | 4.2          | Translation Method                                                                                        | 52  |  |

|               |              | 4.2.1 Event Mapping Functions                                                                             | 53  |  |

|               |              | 4.2.2 Output Equivalence                                                                                  | 54  |  |

|          |     | $4.2.3 \\ 4.2.4$ | Centralized Controller                                           | $\begin{array}{c} 57 \\ 63 \end{array}$ |

|----------|-----|------------------|------------------------------------------------------------------|-----------------------------------------|

| <b>5</b> | Con | ntrol ai         | nd Nonblocking Verification                                      | 73                                      |

|          | 5.1 |                  | visory Control Construction                                      | 73                                      |

|          | 5.2 | Map V            | / Is Well Defined                                                | 80                                      |

|          | 5.3 | Superv           | visory Control and SD Supervisors                                | 83                                      |

|          | 5.4 | Concu            | rrent Supervisory Control Equivalent                             | 100                                     |

| 6        | Syn |                  | Verification for SD System                                       | 113                                     |

|          | 6.1 | Predic           | eates and Predicate Transformers                                 | 113                                     |

|          |     | 6.1.1            | State Predicates                                                 | 113                                     |

|          |     | 6.1.2            | Predicate Transformers                                           | 115                                     |

|          | 6.2 | Symbo            | blic Representation                                              | 116                                     |

|          |     | 6.2.1            | State Subsets                                                    | 116                                     |

|          |     | 6.2.2            | Transitions                                                      | 117                                     |

|          | 6.3 | Symbo            | blic Computation                                                 | 119                                     |

|          |     | 6.3.1            | Transitions and Inverse Transitions                              | 119                                     |

|          |     | 6.3.2            | Computation of Predicate Transformers                            | 121                                     |

|          | 6.4 | v                | blic Verification                                                | 123                                     |

|          |     | 6.4.1            | Untimed Controllability                                          | 124                                     |

|          |     | 6.4.2            | Plant Completeness                                               | 126                                     |

|          |     | 6.4.3            | Non-blocking                                                     | 127                                     |

|          |     | 6.4.4            | Activity Loop Free                                               | 127                                     |

|          |     | 6.4.5            | Proper Time Behavior                                             | 128                                     |

|          |     | 6.4.6            | SD Controllability and S-Singular Prohibitable Behavior $\ldots$ | 129                                     |

| 7        | Exa | mples            |                                                                  | 143                                     |

|          | 7.1 | Exam             | •                                                                | 144                                     |

|          |     | 7.1.1            | Plant Completeness                                               | 144                                     |

|          |     | 7.1.2            | Activity Loop Free                                               | 146                                     |

|          |     | 7.1.3            | Proper Time Behavior                                             | 147                                     |

|          |     | 7.1.4            | SD Controllability                                               | 148                                     |

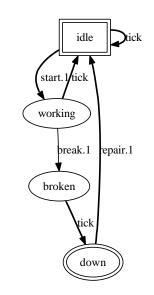

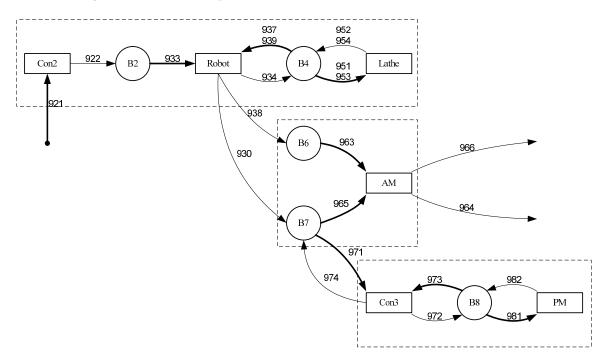

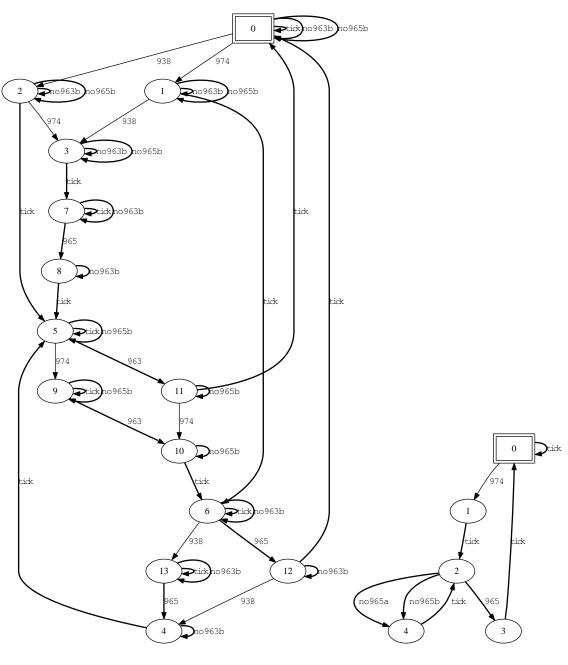

|          | 7.2 |                  | ontrolled Flexible Manufacturing System                          | 156                                     |

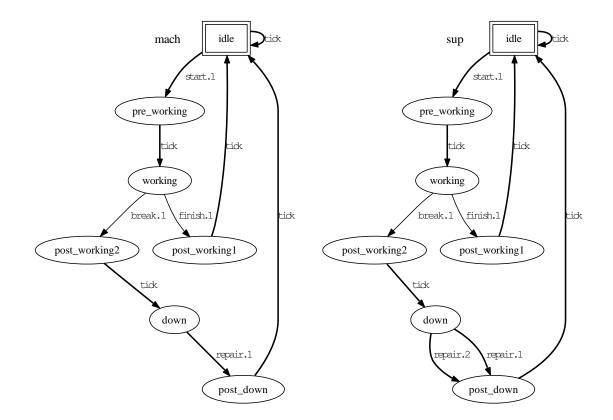

|          |     | 7.2.1            | FMS Plants                                                       | 156                                     |

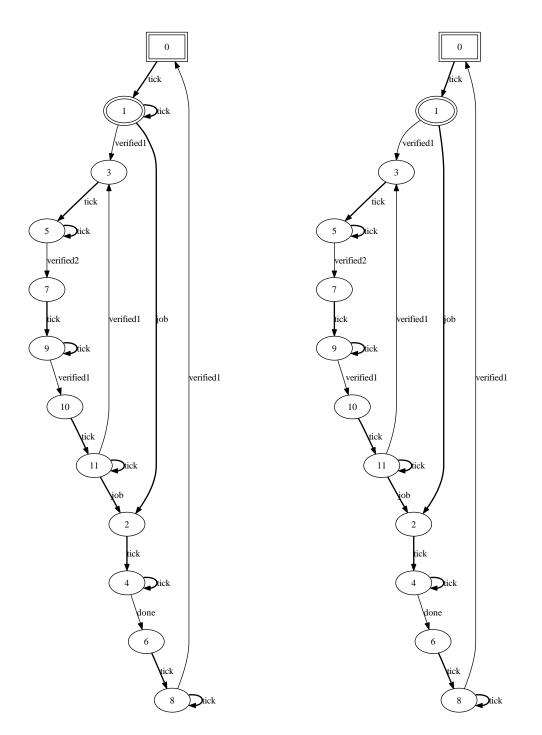

|          |     | 7.2.2            | Buffer Supervisors                                               | 157                                     |

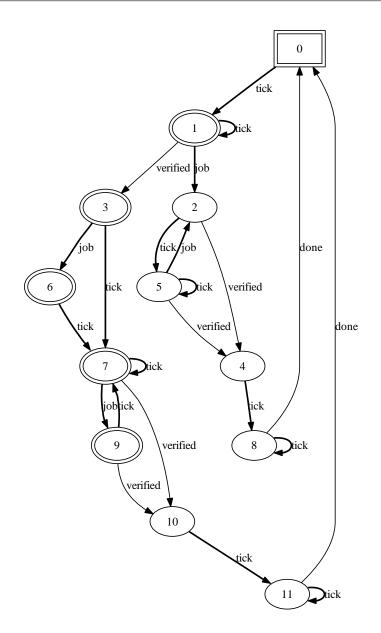

|          |     | 7.2.3            | B4 to Lathe Path                                                 | 161                                     |

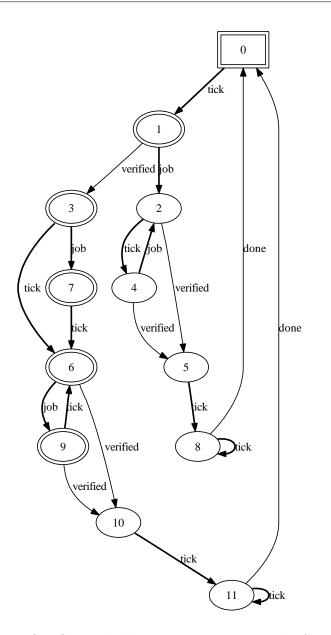

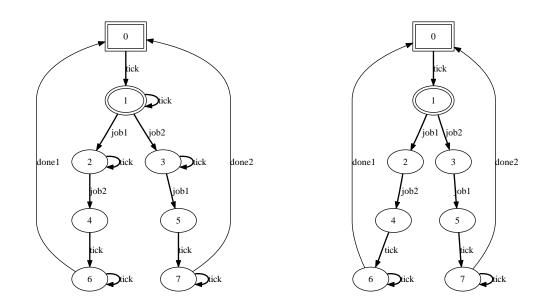

|          |     | 7.2.4            | Moving Parts from B4 to B6/B7                                    | 164                                     |

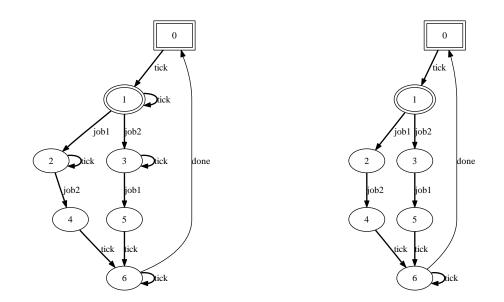

|          |     | 7.2.5            | AM to Exit Path                                                  | 164                                     |

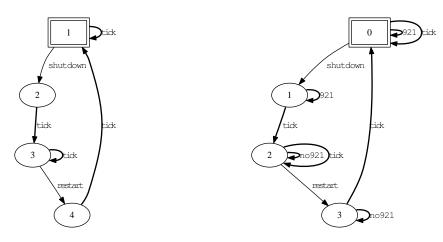

|          |     | 7.2.6            | System Shutdown                                                  | 169                                     |

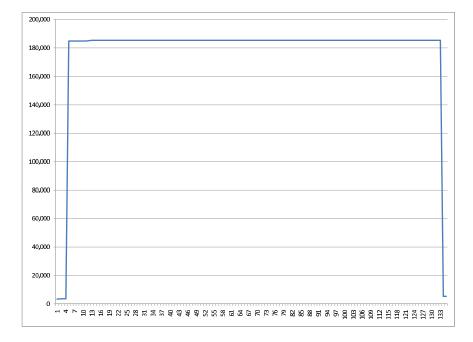

|    |               | 7.2.7  | Algorithm Runtime Statistics                                 | 171 |

|----|---------------|--------|--------------------------------------------------------------|-----|

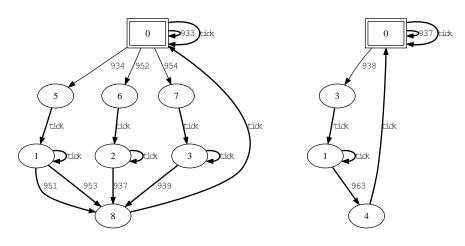

|    | 7.3           | Transl | ating FSM Supervisors to Moore FSM                           | 174 |

|    |               | 7.3.1  | Adding More Timing Information                               | 174 |

|    |               | 7.3.2  | FSM Controllers for Flexible Manufacturing System            | 176 |

| 8  | Con           | clusio | 18                                                           | 183 |

| Bi | bliog         | graphy |                                                              | 187 |

| A  | $\mathbf{SD}$ | Softwa | are Program                                                  | 191 |

|    | A.1           | FMS I  | Example Input Files                                          | 191 |

|    |               | A.1.1  | FMS Plants                                                   | 191 |

|    |               | A.1.2  | Helper Plants                                                | 195 |

|    |               | A.1.3  | Buffer Supervisors                                           | 197 |

|    |               | A.1.4  | Additional Supervisors                                       | 201 |

|    | A.2           | Source | e code                                                       | 208 |

|    |               | A.2.1  | Main                                                         | 209 |

|    |               | A.2.2  | Global Functions, Typedefs, Variables, Preprocessors symbols | 216 |

|    |               | A.2.3  | DES Class                                                    | 235 |

|    |               | A.2.4  | Sub Class                                                    | 256 |

|    |               | A.2.5  | LowSub Class                                                 | 299 |

|    |               |        |                                                              |     |

# List of Figures

| 1.1  | The Occurrences of Two Events                                           |

|------|-------------------------------------------------------------------------|

| 2.1  | An Example DES                                                          |

| 2.2  | An Example Failing ALF Property 24                                      |

| 2.3  | An Example Failing the Proper Time Behavior Property                    |

| 3.1  | Nonminimal Example                                                      |

| 3.2  | An Example for <b>Point ii</b>                                          |

| 3.3  | An Example for <b>Point iii.1</b>                                       |

| 3.4  | An Example Failing <b>Point iv</b>                                      |

| 3.5  | SD Controllability and Arbitrary Union                                  |

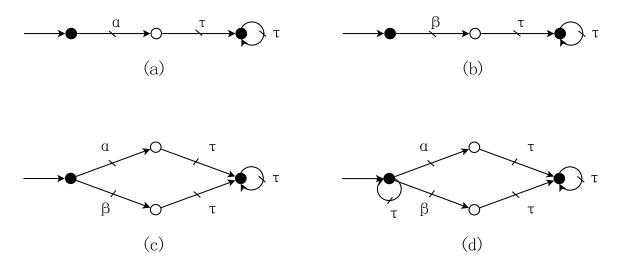

| 4.1  | FSM Translation Example 51                                              |

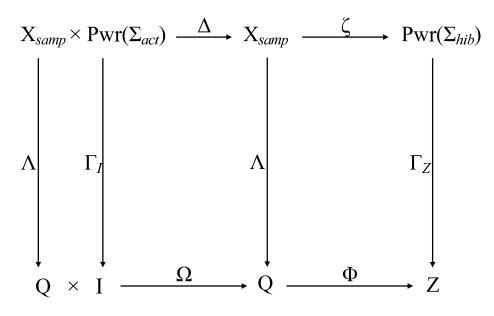

| 4.2  | Centralized Control Equivalence Diagram                                 |

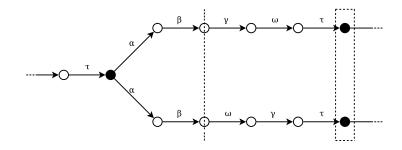

| 5.1  | An Example Failing <b>S</b> -singular Prohibitable Behavior Property 74 |

| 5.2  | Part of a TDES plant                                                    |

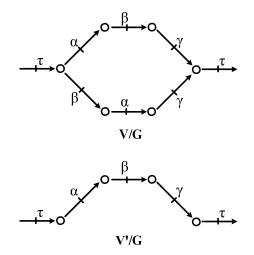

| 5.3  | An Example for Concurrent Supervisory Control Equivalence 102           |

| 7.1  | Legend Used to Display DES                                              |

| 7.2  | Plant Completeness Example: Plant                                       |

| 7.3  | Plant Completeness Example: Supervisor                                  |

| 7.4  | Activity Loop Example                                                   |

| 7.5  | Proper Time Behavior Example                                            |

| 7.6  | SD Controllability i, ii Example: Plant                                 |

| 7.7  | SD Controllability Point i, ii Example: Supervisor                      |

| 7.8  | SD Controllability Point iii.1 Example: Plant                           |

| 7.9  | SD Controllability Point iii.1 Example: Supervisor                      |

| 7.10 | SD Controllability Point iii.2 Example: Plant                           |

| 7.11 | SD Controllability Point iii.2 Example: Supervisor                      |

| 7.12 | SD Controllability Point iv Example: Plant 155                          |

| 7.13 | SD Controllability Point iv Example: Supervisor                                                                                               | 155 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | Flexible Manufacturing System Overview                                                                                                        | 156 |

|      | Conveyor - Con2                                                                                                                               | 157 |

|      | Robot                                                                                                                                         | 157 |

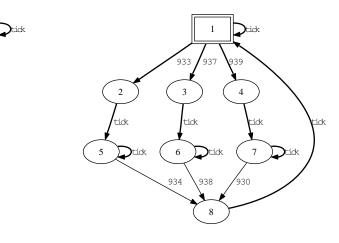

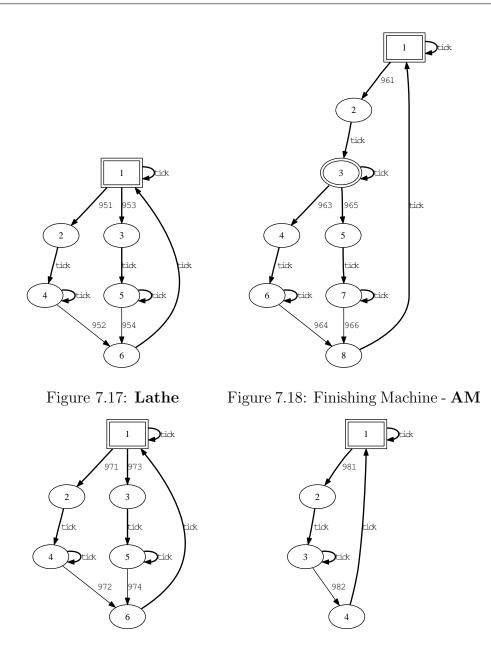

| 7.17 | Lathe                                                                                                                                         | 158 |

|      | Finishing Machine - $\mathbf{AM}$                                                                                                             | 158 |

|      | Conveyor - Con3                                                                                                                               | 158 |

|      | Painting Machine - <b>PM</b>                                                                                                                  | 158 |

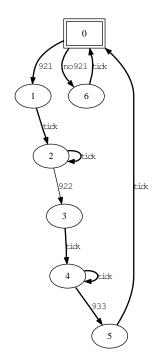

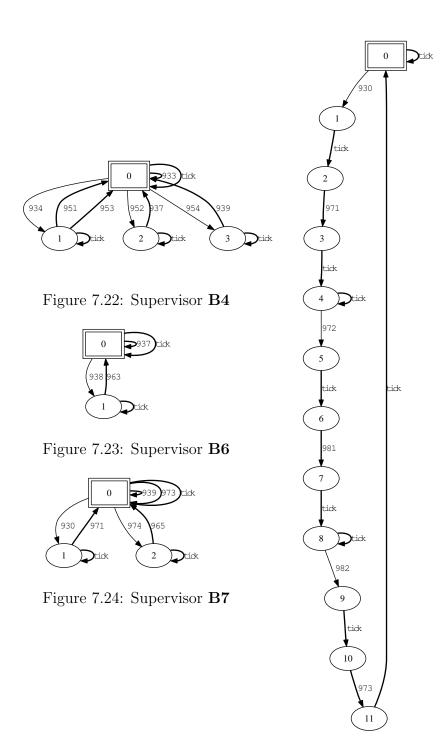

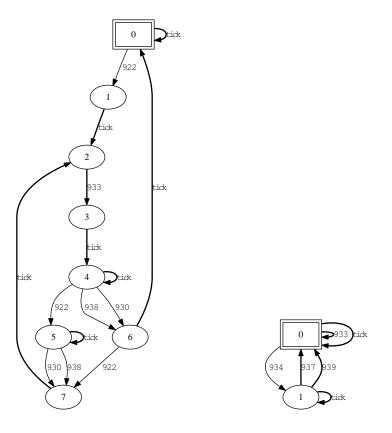

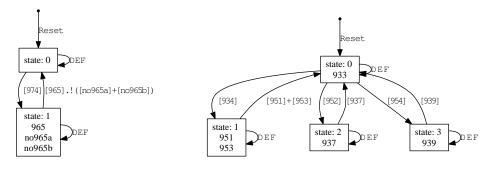

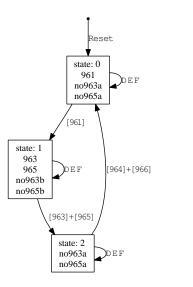

| 7.21 | Supervisor <b>B2</b>                                                                                                                          | 159 |

| 7.22 | Supervisor $\mathbf{B4}$                                                                                                                      | 160 |

| 7.23 | Supervisor $\mathbf{B6}$                                                                                                                      | 160 |

| 7.24 | Supervisor $\mathbf{B7}$                                                                                                                      | 160 |

| 7.25 | Supervisor $\mathbf{B8}$                                                                                                                      | 160 |

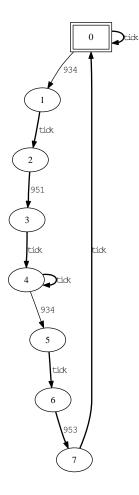

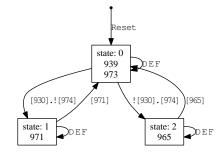

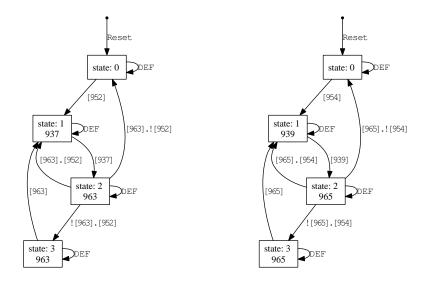

| 7.26 | $TakeB2 \ldots \ldots$ | 162 |

|      | B4Path                                                                                                                                        | 162 |

| 7.28 | LathePick                                                                                                                                     | 163 |

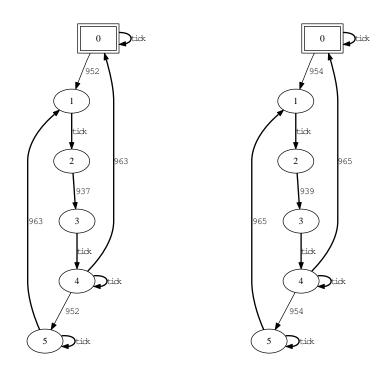

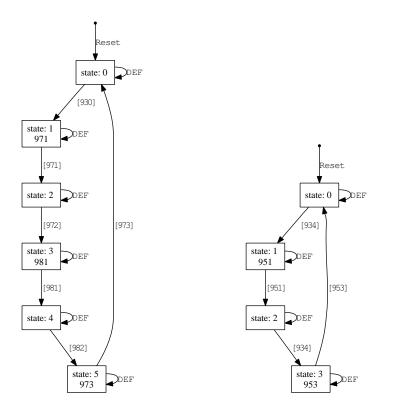

|      | TakeB4PutB6                                                                                                                                   | 165 |

|      | TakeB4PutB7                                                                                                                                   | 165 |

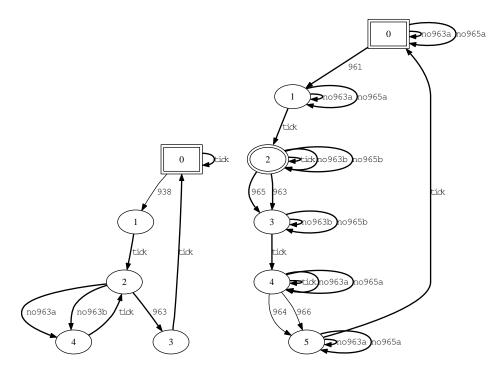

| 7.31 | Plant AddNo963                                                                                                                                | 166 |

| 7.32 | Plant AddNo965                                                                                                                                | 166 |

| 7.33 | Force963                                                                                                                                      | 167 |

|      | Force961                                                                                                                                      | 167 |

| 7.35 | AMChooser                                                                                                                                     | 168 |

| 7.36 | Force965                                                                                                                                      | 168 |

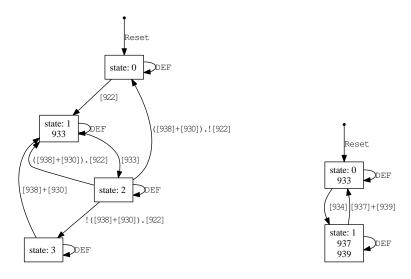

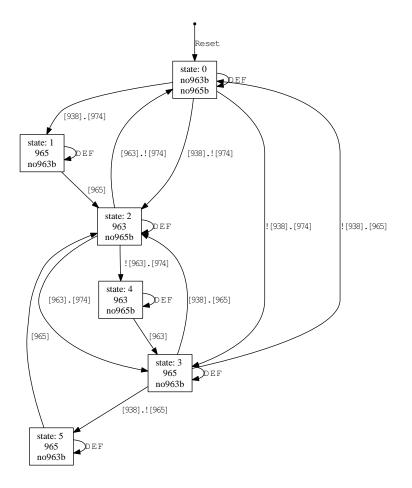

| 7.37 | Plant SystDownNup                                                                                                                             | 170 |

|      | Supervisor handleSystDown                                                                                                                     | 170 |

| 7.39 | Plant AddNo921                                                                                                                                | 170 |

| 7.40 | Histogram for Memory Usage (Kbytes vs. seconds)                                                                                               | 173 |

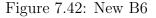

| 7.41 | New B4                                                                                                                                        | 175 |

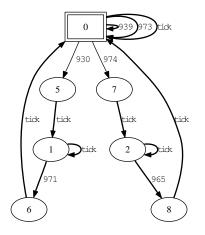

| 7.42 | New B6                                                                                                                                        | 175 |

| 7.43 | New B7                                                                                                                                        | 175 |

| 7.44 | New B4Path                                                                                                                                    | 175 |

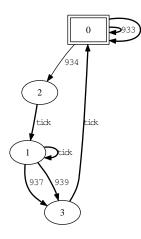

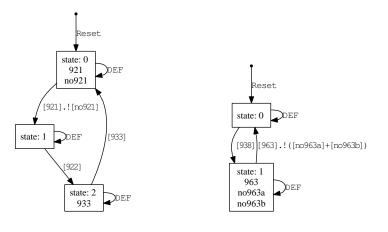

| 7.45 | FSM B2                                                                                                                                        | 178 |

| 7.46 | FSM Force963                                                                                                                                  | 178 |

| 7.47 | FSM Force965                                                                                                                                  | 178 |

| 7.48 | FSM B4                                                                                                                                        | 178 |

| 7.49 | FSM B6                                                                                                                                        | 179 |

| 7.50 | FSM B7                                                                                                                                        | 179 |

| 7.51 | FSM B8                                                                                                                                        | 180 |

| 7.52 | FSM LathePick                                                                                                                                 | 180 |

| 7.53 | FSM TakeB2 1                                                                                                                        | 180 |

|------|-------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.54 | FSM B4Path 1                                                                                                                        | 180 |

| 7.55 | FSM Force961                                                                                                                        | 181 |

| 7.56 | FSM handleSystDown 1                                                                                                                | 181 |

| 7.57 | $FSM TakeB4PutB6 \dots \dots$ | 181 |

| 7.58 | FSM TakeB4PutB7                                                                                                                     | 181 |

| 7.59 | FSM AMChooser                                                                                                                       | 182 |

## Chapter 1

## Introduction

In the area of Discrete-Event Systems (DES) [23], [29], [30], a lot of effort has been devoted to studying standard properties such as nonblocking (a form of deadlock detection) and controllability (a check on whether we can actually realize our desired control law) in a theoretical setting. However, limited effort has been made in investigating what an implementation of a DES supervisor would be like, how to do the conversion automatically, whether we can guarantee that it will retain the controllability and nonblocking properties of the theoretical supervisor, and how to handle timing delay and concurrency issues inherent in an implementation. This thesis will be attacking these problems, although issues with respect to timing delay will only be partially dealt with due to time limitations.

A logical implementation method for DES supervisors would be sampled-data (SD) controllers. An SD controller is driven by a periodic clock and sees the system as a series of inputs and outputs. On each clock edge, it samples its inputs, changes state, and updates its outputs. An example of an SD controller might be a programmable logic controller (PLC) [4] or a Moore synchronous finite state machine (FSM) [7]. In this thesis, we will focus on FSM SD controllers as they are a complete specification of an SD controller, yet still quite generic allowing an FSM to be implemented in digital logic, or as a computer program. For simplicity, we will assume inputs and outputs of an FSM can take the value of true or false.

When we are using an SD controller to manage a given system, we associate an input with each event, and output with each controllable event. We consider an event to have occurred when its corresponding input has gone true during a given clock period. We consider a controllable event to be enabled when its corresponding output has been set true by the controller, disabled otherwise.

As mentioned above, an SD controller samples the value of its inputs on each clock edge, and uses this value to decide what its next internal state will be. This means the SD controller knows nothing about its inputs until the clock edge, and then all it learns is whether a given input is true or false, signifying that the corresponding event has occurred sometime in the clock period that just ended. This means that for the given clock period, all information about event ordering (which event occurred first etc) is lost, as well as how often a given event occurred if it has occurred more than once. The only ordering information that remains is which *sampling period* (clock period) a given event occurred in.

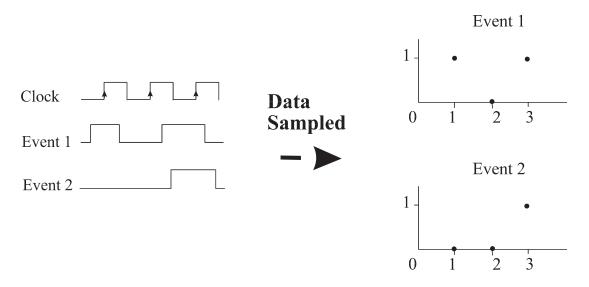

As an example, consider Figure 1.1. Here we have inputs Event 1 and 2, as well as our sampling clock. The diagram on the left shows when the inputs changed their value, in particular that Event 1 occurred first in the second sampling period. When

Figure 1.1: The Occurrences of Two Events

the SD controller samples its inputs, it simply gets a true or false value, based on the value of the input at the clock edge.<sup>1</sup> As we can see in the diagram on the right,

$<sup>^{1}</sup>$ In our example, we are sampling our inputs when the clock signal rises from low to high (the rising edge of the clock).

#### 1. Introduction

the controller simply knows that both Event 1 and 2 occurred in the last sampling period, nothing more.

Another important aspect of an SD controller is that it only changes state on a clock edge, and the value of its outputs are a function of its current state. That means its outputs can only change at a clock edge, and then must stay constant for the rest of the clock period.

For DES supervisors, we generally assume that a supervisor knows immediately when an event occurs, that it can change enablement information right away, and that events occur in an interleaving fashion so the supervisor can always determine the order events occurred in. Based on the above discussion, it is clear that an SD controller implementation violates these assumptions. First, the controller must wait until the next sampling instance (clock edge) before it will know if a given event has occurred. If the control law said something like "once event  $\alpha$  occurs, controllable event  $\beta$  must not occur." However if  $\beta$  can occur in the same sampling period as  $\alpha$ ,  $\beta$  may have already occurred before we even know that  $\alpha$  has occurred. Of course, even if we did know right away that alpha had occurred, we would not be able to update the enablement information for  $\beta$  until the next clock edge anyway, which could be too late. If we wanted to make sure  $\beta$  did not occur in this clock period, we would have to disable it at the start of the sampling period. This means that we cannot enforce a policy where an event is initially enabled (disabled) at the start of a clock period, and we then disable (enable) the event somewhere in the middle. Our supervisor must have a policy that is correct and constant for the entire sampling period.

Another important issue is event ordering. If we could get either string ' $\alpha\beta$ ' or ' $\beta\alpha$ ' in the same clock period, our SD controller would only know that at least one  $\alpha$  and at least one  $\beta$  had occurred. It would not know which of the two had actually occurred. If our DES supervisor enabled event  $\gamma$  when string ' $\alpha\beta$ ' occurs, but disables  $\gamma$  when string ' $\beta\alpha$ ' occurs, we could not implement this using an SD controller as it would not be able to determine which of the two strings had occurred. This means that a supervisor must always do the same thing for two concurrent strings containing the same individual events, both immediately after the strings have occurred and in the future. Of course, this raises the question of how to determine if two strings are concurrent.

## 1.1 Objective

Clearly, untimed DES does not provide a rich enough modeling method to allow us to work with an SD controller, and its inherent timing information. Therefore, we will base our work on the timed DES (TDES) theory developed by Brandin et al. [5] [6]. TDES extends untimed DES theory by adding a new tick event, corresponding to the tick of a global clock. The event set of a TDES contains the tick event as well as other non-tick events called *activity* events. The occurrence of a tick event provides us with a concept of time passing, allowing us to model upper and lower time bounds for the occurrence of activity events. It also allows us to introduce a new type of events called *forcible events*, which we can guarantee to occur and preempt the next clock tick. This means that now we cannot only prevent some events (referred to as *prohibitable events* in TDES terminology) from occurring by disabling them, but we can also choose to have certain events occur before the next clock tick.

To make the TDES theory work with SD controllers, we identify a tick event occurring with the clock edge that the SD controller uses for sampling and state change. That means that once a tick event occurs, any two strings that are now possible in the system and only contain a single tick at the end of the string, are considered concurrent. We will refer to such strings as *concurrent strings*. If one of these strings contains at least one different event from the other string, we can distinguish between them. Otherwise, we must treat them the same.

Now that we can force an event to occur in a specific clock period, we have a new concern with respect to nonblocking. The plant model might say that we can do either an ' $\alpha\beta\tau$ ' concurrent string, or a ' $\beta\alpha\tau$ ' string, where  $\tau = tick$ . Both might be safe to do, but depending on our implementation, only one of the two might ever occur. Some reasons this could occur are due to time delay, or our implementation might be a sequential program that must choose one version or the other to perform. It might be the case that for some implementations, when two or more concurrent strings are possible and they contain the same events but in a different order or numbers, not all variations might ever actually occur. The problem is that one of the variations that does not occur might have been the only path in the TDES back to a marked state. Basically, if an SD controller cannot tell the difference between concurrent strings, they should have the same marked future. This also means that marked strings can

#### 1. Introduction

only be the empty string (represents the initial state of the system which is always observable), or strings ending in a tick as these are the points in the system's behavior that are observable to an SD controller. We refer to such strings as *sampled strings*.

The next problem we intend to address is the issue of when a forced event should occur. As noted by Balemi in [2] for untimed systems, controllable events tend to be events fully under the control of our controller implementation.<sup>2</sup> They may be a software function we call, an output we set to true, or a message we send. That means that we can make these events occur whenever we want. It is not unusual that a plant might be modeled such that these events are suppose to only occur under certain situations. This might be for flexibility (some implementations have these restrictions, for example) or to make the system easier to model or understand. However, the reality for some controller implementations is that these events. When we are forcing an event to occur in a given clock period, we have no information on when it will actually occur. Depending on our implementation, it could occur right away, or in the middle or end of the clock period. We need to make sure that when it finally does occur, it does not contradict the plant model so that our implementation will correspond to the theoretical model in this respect.

The last issue we intend to address is the issue of when a forcible event should actually occur. We want our supervisor specified in such a way that it is straightforward to convert it into an SD controller. Normally for DES systems, we are interested in maximally permissive behavior. We enable all controllable events except for when they must be disabled to enforce our control law, and to ensure the system is nonblocking. However, controller implementations are usually much more procedural. We would disable all controllable events until we want them to occur, and then disable the event again once it has occurred. In our setup, we will be assuming that the set of prohibitable events and forcible events are the same<sup>3</sup> and that we disable the event until we wish to force it, and then disable it once it has occurred. This

$<sup>^{2}</sup>$ This is generally a matter of how a system is modeled. We can always model the sending of our enable/disable signal as the controllable event, and the occurrence of the actual action as the uncontrollable event. Of course, the occurrence of the enablement event would toggle the eligibility of the uncontrollable event.

<sup>&</sup>lt;sup>3</sup>Again, this is a matter of modeling. We can always model our forcing signal as the controllable event, and then model the event corresponding to the actual action as an uncontrollable event that must occur before the next clock tick, once the forcing event has occurred.

requires our supervisor to specify exactly which clock period the event should occur in and this makes it very straight forward to translate to a controller. Currently, a supervisor could say something like controllable event  $\alpha$  is now enabled, and will stay enabled for the next three clock cycles, but must occur before the fourth. You could potentially force it sooner, but that might cause blocking. Such an ambiguous supervisor will be a lot harder to translate to an SD controller.

In this thesis, we will develop a new property for TDES systems that will address the above issues, as well as make our TDES supervisor more consistent with SD controllers, making them easy to translate. First, we will provide the preliminaries of untimed and timed DES in Chapter 2, which is required to understand the following chapters.

Then in Chapter 3 we will introduce the sampled-data setting based on timed DES. The sampled-data setting will be formally defined, and we will develop a new property called SD controllability to address the issues we identified above.

In Chapter 4, we will provide the definition of Moore FSM [17] and a method to translate a CS deterministic supervisor (defined in Chapter 3) into a Moore FSM controller. We will present both a centralized translation method and a modular method. We will then show that they will both produce equivalent output information.

Then in Chapter 5 we capture the enablement and forcing action of a translated controller in the form of a TDES supervisory control map, and show that the closed loop behavior of this map and the plant is the same as that of the plant and the original TDES supervisor. We also show that our method is robust with respect to nonblocking and certain variations in the actual behavior of our physical system.

In Chapter 6 we will introduce logic predicates and predicate transformers, as well as symbolic representation and computation based on [26]. Then we will introduce a set of algorithms to verify SD controllability and other properties of interest to us.

Then in Chapter 7 we will present examples which fail the key conditions in this thesis, to help understand the definitions. We will then present a successful application example inspired by the untimed Flexible Manufacturing System from [11], including the Moore FSM controllers translated from the supervisors developed in the example.

We will close the thesis with our conclusions and a brief discussion of future work. Also, in the appendix we will present the input files used for the FSM example given in Chapter 7, as well as the source code for our software tool that we have developed that implements the algorithms presented in Chapter 6. The software tool makes use of binary decision diagrams (BDD) [8].

### 1.2 Related Work

Supervisory control of DES with timing information, known as timed DES (TDES), was firstly introduced in [5], [6], based on the timed transition model from [19], [20], and [21]. The theory added timing information to supervisory control allowing one to specify lower and upper time bounds for events. It also introduced a forcing technology to ensure certain events occur when we desired. We will use this as the basis of our SD supervisory control theory.

Balemi [2] pointed out that typically, controllable events are part of the supervisor implementation, and often can occur whenever we want them to. For simplicity, the plant may be modeled such that these events are assumed to only occur at certain times. Balemi's plant completeness condition helps ensures that the implementation of the supervisor will be consistent with the plant model so that controllable events do not occur when the plant model says that they cannot.

In the sampled-data setting, if the same event occurs once or multiple times in the same sampling period, an SD controller will not be able to detect a difference. In [3], the authors require that the system has the property that an event cannot be generated more than once during a sampling period. The paper also discussed the loss of ordering information when events occur in the same sampling period. To handle these timing related issues, the author adds a dispatcher to the existing supervisor to solve the problems that could occur when event ordering cannot be ignored. The model is implemented based on Petri Nets [16, 33] and an algorithm to translate the Petri Net implementation into computer language is provided.

Translating abstract model into a computer understandable form is an interesting topic for researchers. In [12], Leduc discusses the modeling and implementation of real-life DES problems as well. Theorems for model reduction were created and applied to the DES designed for a programmable logic controller (PLC) based manufacturing testbed. The author investigated implementing DES as Moore finite state machines (FSM) and created an implementation by hand for the testbed. As mentioned earlier, FSM can be converted to other forms of state based logic sequences, such as a relay ladder logic program for the testbed. The idea of implementing SD controllers as FSM is motivated by this thesis.

Similarly, [18] also discusses translating DES into PLC programs. The difference is that they first convert automata into the Grafcet language, which describes the specification of logic controllers. They then translate the Grafcet language into a PLC program. Both [12] and [18] uses automated manufacturing testbeds as examples.

In [9], DES theory is used as a tool to assist programming in the system control area. The authors describe an approach to generate Java code for concurrency control automatically. The approach formalizes each individual code portion without concurrency control into specifications, builds the DES model, and then generates the code with verifications.

A real world application of DES supervisory control is given in [10], where Petri Nets are used to model railway networks and ensure controllability and liveness.

An important tool to allow supervisory control methods to be applied to larger systems, is the use of binary decision diagrams (BDD)[8]. BDD methods have been applied to standard DES [32], [27], state tree structures [14], Hierarchical Interfacebased Supervisory Control [26], and state based control of TDES [24].

When synthesizing controllers there is often a need to consider other components in the system, which lower the flexibility and increase the cost of synthesis in changing environments. With the I/O based hierarchical structure from [22], each controller can be designed independently, and controllability and nonblocking is retained when the controllers are combined.

However, even if the DES supervisor is nonblocking for the DES plant does not mean that the controller implementation is nonblocking as well. To ensure a controller is nonblocking, [15] studied several different systems for implementing controllers. The author suggested conditions to be satisfied for the implemented controllers to be nonblocking.

Another practical issue in implementing controllers based on DES is communication. In [25], the authors study the communication between modular and decentralized supervisors on switch networks. A communication model is then introduced for a large distributed controller network where communication delay and collisions are a concern. In [31], the authors resolve communication issues by introducing an asynchronous implementation. The work formalizes the delay between the controller and the plant, and defines bounded-delay implementability, in addition to the standard controllability and nonblocking properties. \_\_\_\_\_

## Chapter 2

# Discrete-Event Systems Preliminaries

Supervisory control theory provides a framework for the control of discrete-event systems (DES), systems that are discrete in space and time. For a detailed exposition of DES, see [29]. Below, we present a summary of the terminology that we use in this thesis.

### 2.1 Algebraic Preliminaries

### 2.1.1 Strings

An alphabet  $\Sigma$  is defined to be a finite set of distinct symbols. A string over  $\Sigma$  is a finite sequence of symbols  $\sigma_1 \sigma_2 ... \sigma_k$ , where  $\sigma_i \in \Sigma$  for i = 1, 2, ..., k. Given a string  $s = \sigma_1 \sigma_2 ... \sigma_k$ , |s| = k is the length of the string. The string  $\epsilon$  is called the *empty string* with  $|\epsilon| = 0$ . Let  $\Sigma^*$  be the set of all finite symbol sequences and define  $\Sigma^+$  be

$$\Sigma^+ := \Sigma^* - \{\epsilon\}$$

**Definition 2.1.1.** Let  $s_1, s_2 \in \Sigma^*$ , where  $s_1 = \sigma_1 \sigma_2 \dots \sigma_m$  and  $s_2 = \tau_1 \tau_2 \dots \tau_n$ . The *catenation* of  $s_1$  and  $s_2$  is define to be *cat* :  $\Sigma^* \times \Sigma^* \to \Sigma^*$  such that

$$cat(s_1, \epsilon) = cat(\epsilon, s_1) = s_1 = \sigma_1 \sigma_2 ... \sigma_m$$

$$cat(s_1, s_2) = s_1 s_2 = \sigma_1 \sigma_2 ... \sigma_m \tau_1 \tau_2 ... \tau_n$$

As  $|s_1| = m$  and  $|s_2| = n$ , the length of concatenated string is  $|s_1s_2| = |s_1| + |s_2| = m + n$ .

**Definition 2.1.2.** Let  $s, t \in \Sigma^*$ . We say s is a *prefix* of t, denoted as  $s \leq t$ , if

$$(\exists u\in\Sigma^*)su=t$$

By definition, we can see that a string  $s \in \Sigma^*$  is a prefix of itself, as  $s \leq s$ . Also,  $\epsilon$  is a prefix of all strings, as  $(\forall s \in \Sigma^*) \epsilon \leq s$ .

#### 2.1.2 Languages

**Definition 2.1.3.** Let  $L \subseteq \Sigma^*$ . The *prefix closure* of L, denoted as  $\overline{L}$ , is defined as

$$\overline{L} = \{ s \in \Sigma^* | (\exists t \in L) s \le t \}$$

By definition, we can see that a language L is a subset of the prefix closure of itself, i.e.  $L \subseteq \overline{L}$ . We say a language  $L \subseteq \Sigma^*$  is *prefix closed* if  $L = \overline{L}$ . Let  $K \subseteq L$ . We say K is L-closed if  $K = \overline{K} \cap L$ .

**Definition 2.1.4.** Let  $L \subseteq \Sigma^*$ . The *eligibility operator*,  $\operatorname{Elig}_L : \Sigma^* \to \operatorname{Pwr}(\Sigma)$ , is defined for  $s \in \Sigma^*$  as,

$$\operatorname{Elig}_{L}(s) := \{ \sigma \in \Sigma \mid s\sigma \in L \}$$

### 2.1.3 Nerode Equivalence Relation

**Definition 2.1.5.** Let X be a nonempty set. Let  $E \subseteq X \times X$  be a binary relation on X. The relation E is an *equivalence relation* on X if

- 1.  $(\forall x \in X) x E x$  (reflexivity)

- 2.  $(\forall x, x' \in X) x E x' \implies x' E x$  (symmetry)

- 3.  $(\forall x, x', x'' \in X) x E x' \& x' E x'' \implies x E x'' \text{ (transitivity)}^1$

<sup>&</sup>lt;sup>1</sup>We use '&' to stand for logical AND here to avoid confusion with later definitions in this section.

Here we are using standard infix notation, where we use xEx' to represent the ordered pair  $(x, x') \in E$ . For xEx', we may also write  $x \equiv x' \pmod{E}$ .

For  $x \in X$ , let  $[x]_E \subseteq X$  represent the subset of elements that are equivalent mod E to x. That is

$$[x]_E := \{x' \in X | x'Ex\}$$

If relation E is understood by the context, we will just write [x]. We will also refer to [x] as the coset or the equivalence class of x with respect to E.

Let  $s, t \in \Sigma^*$ , and  $L \subseteq \Sigma^*$ . We say s and t are *Nerode equivalent* with respect to language L, if and only if they can be extended by any string  $u \in \Sigma^*$  such that the two extended strings are either both in L or neither in L. In this case, we write  $s \equiv t$ (mod L) or  $s \equiv_L t$ . The formal definition is given below.

**Definition 2.1.6.** Let  $L \subseteq \Sigma^*$ . Let  $s, t \in \Sigma^*$ .

$$s \equiv_L t \text{ or } s \equiv t \pmod{L}$$

iff

$$(\forall u \in \Sigma^*) su \in L \iff tu \in L$$

Essentially, if strings s and t are equivalent mod L, then they can both be extended in the same way by right concatenation.

**Example 2.1.** Let  $\Sigma = \{\alpha, \beta, \gamma\}$ ,  $L = \{\epsilon, \alpha, \beta, \alpha\gamma^*, \beta\gamma^*\}$ , then  $\alpha \equiv_L \beta$ .

### 2.2 Discrete Event Systems

### 2.2.1 Generator

We model DES formally as a generator  $\mathbf{G}$ , which is a five tuple

$$\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$$

where

Q is the state set.

$\Sigma$  is the finite set of distinct symbols representing event labels. We partition  $\Sigma$  into two parts

$$\Sigma = \Sigma_c \mathrel{\dot{\cup}} \Sigma_u$$

where

- $\Sigma_c$  is the set of *controllable* events, which can be enabled or disabled by an external agent. A controllable event can only occur when it is enabled.

- $\Sigma_u$  is the set of *uncontrollable* events, which cannot be disabled by any external agent. Once the DES has reached a state where an uncontrollable event can occur, the event cannot be prevented.

- $\delta: Q \times \Sigma \to Q$  is the (partial) transition function where each transition is a tuple  $(q, \sigma, q')$ , where  $\delta(q, \sigma) = q'$ . We refer to q as the *exit (source) state*, and q' as the *entrance (destination) state*. We write  $\delta(q, \sigma)$ ! if  $\delta(q, \sigma)$  is defined.

We can extend the transition function to  $\delta:Q\times\Sigma^*\to Q$  as

$$\begin{split} \delta(q,\epsilon) &= q \quad \text{for } q \in Q. \\ \delta(q,s\sigma) &= \delta(\delta(q,s),\sigma) \quad \text{for } s \in \Sigma^*, \, \sigma \in \Sigma, \, \text{and} \, q \in Q. \end{split}$$

as long as  $q' = \delta(q, s)!$  and  $\delta(q', \sigma)!$ .

$q_0 \in Q$  is the *initial state*.

$Q_m \subseteq Q$  is the subset of marked states.

We can extend the transition function to  $\delta:Q\times\Sigma^*\to Q$  as

$$\begin{split} &\delta(q,\epsilon)=q \quad \text{for } q\in Q. \\ &\delta(q,s\sigma)=\delta(\delta(q,s),\sigma) \quad \text{for } s\in \Sigma^*, \, \sigma\in \Sigma, \, \text{and} \, q\in Q \end{split}$$

as long as  $q' = \delta(q, s)!$  and  $\delta(q', \sigma)!$ .

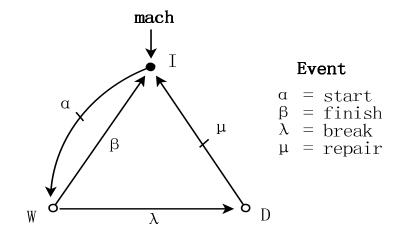

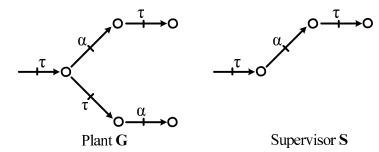

**Example 2.2.** Let  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  be the DES shown in Figure 2.1. By convention, a controllable event is graphically represented by a slash across its transition

arrow. Marked states are represented by a black dot. The state pointed at by an arrow with no exit state, is the initial state. For the DES shown we have:

$$Q = \{I, W, D\};$$

$$\Sigma = \Sigma_c \ \cup \ \Sigma_u, \ where \ \Sigma_c = \{\alpha, \mu\} \ and \ \Sigma_u = \{\beta, \lambda\};$$

$$\delta = \{(I, \alpha, W), (W, \beta, I), (W, \lambda, D), (D, \mu, I)\};$$

$$q_0 = I; \ Q_m = \{I\}$$

Figure 2.1: An Example DES

Given DES  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$ , we have the following definitions.

**Definition 2.2.1.** A state  $q \in Q$  is *reachable* if

$$(\exists s \in \Sigma^*) \delta(q_0, s)!$$

and  $q = \delta(q_0, s)$

**Definition 2.2.2.** A state  $q \in Q$  is *coreachable* if

$$(\exists s \in \Sigma^*) \delta(q, s)!$$

and  $\delta(q, s) \in Q_m$

To simplify the following discussions, we will always assume a given DES is reachable unless explicitly stated otherwise.

Definition 2.2.3. The *closed behavior* of DES G is

$$L(\mathbf{G}) = \{s \in \Sigma^* | \delta(q_0, s)!\}$$

**Definition 2.2.4.** The marked behavior of DES **G** is

$$L_m(\mathbf{G}) = \{ s \in \Sigma^* | \delta(q_0, s)! \& \delta(q_0, s) \in Q_m \}$$

Clearly,  $L_m(\mathbf{G}) \subseteq L(\mathbf{G})$ .

**Definition 2.2.5.** The *control action* for some  $q \in Q$  for DES **G** is defined to be a mapping  $\zeta : Q \to Pwr(\Sigma_c)$  that takes q and returns a set of controllable events enabled at q.

**Definition 2.2.6.** DES **G** is said to be *nonblocking* if every reachable state is also coreachable. This can be expressed as

$$L(\mathbf{G}) = \overline{L_m(\mathbf{G})}$$

**Definition 2.2.7.** Let  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  and let  $\lambda$  be an equivalence relation on Q such that for  $q, q' \in Q$ ,  $q \equiv q' \mod \lambda$  if and only if

1.

$$(\forall s \in \Sigma^*) \delta(q, s)! \iff \delta(q', s)!$$

$$2. \ (\forall s \in \Sigma^*)[\delta(q,s)! \& \ \delta(q,s) \in Q_m] \iff [\delta(q',s)! \& \ \delta(q',s) \in Q_m]$$

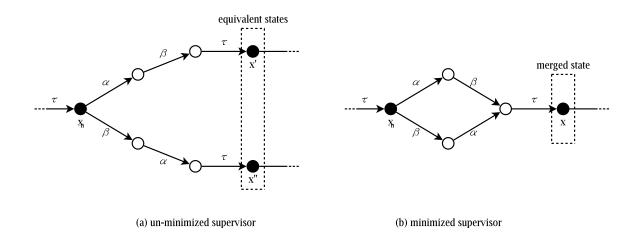

Basically, for states q and q' such that  $q \equiv q' \mod \lambda$ , they have the same future with respect to  $L(\mathbf{G})$  and  $L_m(\mathbf{G})$ . Based on this, for string  $s \in L(\mathbf{G})$ , a state  $q = \delta(q_o, s)$ represents all strings in  $\Sigma^*$  that are equivalent to  $s \mod L(\mathbf{G})$  and  $\mod L_m(\mathbf{G})$ .

**Definition 2.2.8.** DES G is said to be *minimal*, if

$$(\forall q, q' \in Q)q \equiv q' \pmod{\lambda} \iff q = q'$$

It says that for all states  $q, q' \in Q$ , if q is equivalent to  $q' \mod \lambda$ , then q and q' are the same state. DES **G** is minimal if it does not have two distinct states in Q that are  $\lambda$  equivalent.

#### 2.2.2 Synchronization and Product DES

In real world, it is often easier to model a system as several smaller components. For a DES plant, we use the *synchronous product* operator to combine the individual DES components instead of modeling the whole system at once. We first need to define the *natural projection* operator and its inverse.

Let  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  be a DES. Take  $\Sigma_o \subseteq \Sigma$  to be the set of *observable* events through some filtering channel of the events generated by  $\mathbf{G}$ .

**Definition 2.2.9.** The *natural projection*  $P : \Sigma^* \to \Sigma_o^*$  is defined as follows. For  $s \in \Sigma^*, \sigma \in \Sigma$ ,

$$P(\epsilon) = \epsilon$$

$$P(\sigma) = \begin{cases} \epsilon & \text{if } \sigma \notin \Sigma_o \\ \sigma & \text{if } \sigma \in \Sigma_o \end{cases}$$

$$P(s\sigma) = P(s)P(\sigma)$$

**Example 2.3.** For  $\Sigma = \{\alpha, \beta, \gamma\}$ ,  $\Sigma_o = \{\alpha, \beta\}$  and  $s = \alpha \beta \alpha \gamma \beta \alpha$ ,

$$P(s) = P(\alpha)P(\beta)P(\alpha)P(\gamma)P(\beta)P(\alpha) = \alpha\beta\alpha\beta\alpha$$

Let  $L \subseteq \Sigma^*$ . We define  $P(L) \subseteq \Sigma_o^*$  as an extension of the natural projection as

$$P(L) := \{P(s) | s \in L\}$$

We also define its inverse image  $P^{-1}: \operatorname{Pwr}(\Sigma_o^*) \to \operatorname{Pwr}(\Sigma^*)$  such that, for  $H \subseteq \Sigma_o^*$

$$P^{-1}(H) := \{ s \in \Sigma^* | P(s) \in H \}$$

**Example 2.4.** For  $\Sigma = \{\alpha, \beta, \gamma, \mu\}$ ,  $\Sigma_o = \{\alpha, \beta\}$  and  $s_o = \alpha\beta\alpha\beta\alpha$ , the inverse projection is

$$P^{-1}(\{s_o\}) := \{\gamma, \mu\}^* \alpha \{\gamma, \mu\}^* \beta \{\gamma, \mu\}^* \alpha \{\gamma, \mu\}^* \beta \{\gamma, \mu\}^* \alpha \{\gamma,$$

**Definition 2.2.10.** For i = 1, 2, let  $L_i \subseteq \Sigma_i^*$ ,  $\Sigma = \Sigma_1 \cup \Sigma_2$  and  $P_i : \Sigma^* \to \Sigma_i^*$  be natural projections. The synchronous product of  $L_1$  and  $L_2$  is defined to be

$$L_1||L_2 = P_1^{-1}(L_1) \cap P_2^{-1}(L_2)$$

= {s \in \Sigma^\*|P\_1(s) \in L\_1 \& P\_2(s) \in L\_2}

**Definition 2.2.11.** Let  $\mathbf{G}_1 = (Q_1, \Sigma, \delta_1, q_{o,1}, Q_{m,1})$  and  $\mathbf{G}_2 = (Q_2, \Sigma, \delta_2, q_{o,2}, Q_{m,2})$ be two DES defined over the same event set  $\Sigma$ . The *product* of two DES is defined as

$$\mathbf{G}_1 \times \mathbf{G}_2 = (Q_1 \times Q_2, \Sigma, \delta_1 \times \delta_2, (q_{o,1}, q_{o,2}), Q_{m,1} \times Q_{m,2})$$

where  $\delta_1 \times \delta_2 : Q_1 \times Q_2 \times \Sigma \to Q_1 \times Q_2$  is defined as

$$(\delta_1 \times \delta_2)((q_1, q_2), \sigma) := (\delta_1(q_1, \sigma), \delta_2(q_2, \sigma))$$

whenever  $\delta_1(q_1, \sigma)!$  and  $\delta_2(q_2, \sigma)!$ .

By Definition 2.2.11, we have  $L(\mathbf{G}_1 \times \mathbf{G}_2) = L(\mathbf{G}_1) \cap L(\mathbf{G}_2)$  and  $L_m(\mathbf{G}_1 \times \mathbf{G}_2) = L_m(\mathbf{G}_1) \cap L_m(\mathbf{G}_2)$

**Definition 2.2.12.** The *meet* of  $\mathbf{G}_1$  and  $\mathbf{G}_2$ , or  $\mathbf{meet}(\mathbf{G}_1, \mathbf{G}_2)$ , is defined to be the reachable subautomaton of the product DES  $\mathbf{G}_1 \times \mathbf{G}_2$ .

**Definition 2.2.13.** The synchronous product of DES  $\mathbf{G}_i = (Q_i, \Sigma_i, \delta_i, q_{o_i}, Q_{m_i})$  (i = 1, 2), denoted  $\mathbf{G}_1 || \mathbf{G}_2$ , is defined to be a reachable DES  $\mathbf{G}$  with event set  $\Sigma = \Sigma_1 \cup \Sigma_2$  and properties:

$$L_m(\mathbf{G}) = L_m(\mathbf{G}_1) || L_m(\mathbf{G}_2), \quad L(\mathbf{G}) = L(\mathbf{G}_1) || L(\mathbf{G}_2)$$

**Definition 2.2.14.** Let **G** be a DES defined over  $\Sigma$  and  $\Sigma'$  be another set of events such that  $\Sigma \cap \Sigma' = \emptyset$ . The *selfloop* operation on **G** is defined as

$$\mathbf{selfloop}(\mathbf{G}, \Sigma') = (Q, \Sigma \cup \Sigma', \delta', q_o, Q_m)$$

where  $\delta': Q \times (\Sigma \cup \Sigma') \to Q$  is a partial function defined as

$$\delta'(q,\sigma) := \begin{cases} \delta(q,\sigma) & \sigma \in \Sigma, \delta(q,\sigma)! \\ q & \sigma \in \Sigma' \\ \text{undefined} & \text{otherwise} \end{cases}$$

For DES  $\mathbf{G}'_i$  (i = 1, 2) defined over event set  $\Sigma_i$ , we will always assume that the synchronous product operator is implemented by first extending each DES to be over  $\Sigma$  by adding selfloops, and then using the meet operator. More formally, we take  $\Sigma = \Sigma_1 \cup \Sigma_2$ , and  $\mathbf{G}_i = \text{selfloop}(\mathbf{G}'_i, \Sigma - \Sigma_i)$ . We then have  $G'_1 || G'_2 = \text{meet}(\mathbf{G}_1, \mathbf{G}_2)$ .

In the algorithms we develop in this thesis, we will always assume all DES are combined with the product DES operator. If a portion of the system is actually combined together using the synchronous product operator as is commonly done for plant components, we will first add selfloops as above, and then use these new DES from then on in our algorithms.

#### 2.2.3 Controllability and Supervision

We will take language K to represent the desired safe behavior of our plant represented by DES  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$ . We want to make sure that the closed loop behavior of the system – that is the behavior of plant  $\mathbf{G}$  under control of K – is a subset of  $\overline{K}$ .

As we mentioned earlier, our system's event set  $\Sigma$  is partitioned into controllable and uncontrollable events. If an undesirable controllable event is possible in **G** that will cause the system to leave the behavior represented by  $\overline{K}$ , we disable it and prevent it from occurring. We cannot do this with an uncontrollable event, so we need to make sure the plant never reaches a state where it can leave the desired behavior by an uncontrollable event. We now express this formally below.

**Definition 2.2.15.** K is said to be *controllable* with respect to **G** if

$$(\forall s \in \overline{K})(\forall \sigma \in \Sigma_u) s \sigma \in L(\mathbf{G}) \implies s \sigma \in \overline{K}$$

We typically give this definition in the form of  $\overline{K}\Sigma_u \cap L(\mathbf{G}) \subseteq \overline{K}$  where  $\overline{K}\Sigma_u$ denotes the string  $s\sigma$  for  $s \in \overline{K}$  and  $\sigma \in \Sigma_u$ . In other words, if the plant reaches a state where uncontrollable event  $\sigma$  is possible, then  $\sigma$  must also be accepted by  $\overline{K}$ . By definition,  $\emptyset$ ,  $L(\mathbf{G})$  and  $\Sigma^*$  are all controllable with respect to  $\mathbf{G}$ .

Another way to express this definition is

$$(\forall s \in \overline{K} \cap L(\mathbf{G})) \operatorname{Elig}_{L(\mathbf{G})}(s) \cap \Sigma_u \subseteq \operatorname{Elig}_{\overline{K}}(s)$$

which is used in **Point i** of Definition 3.2.1 in Section 3.2.

As we prefer to work with finite state automata than typically infinite languages, we want to be able to express K as a DES supervisor.

**Definition 2.2.16.** Let  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  be a DES. Let  $K \subseteq \Sigma^*$ . We say  $\mathbf{G}$  represents K if

$$K = L_m(\mathbf{G}) \text{ and } \overline{K} = L(\mathbf{G})$$

**Definition 2.2.17.** Let  $\mathbf{S} = (X, \Sigma, \xi, x_o, X_m)$  be a DES. Let  $K \subseteq \Sigma^*$ , we say  $\mathbf{S}$  implements K, if

$$K = L_m(\mathbf{S}) \cap L_m(\mathbf{G}) \text{ and } \overline{K} = L(\mathbf{S}) \cap L(\mathbf{G})$$

Recall that  $\Sigma = \Sigma_c \cup \Sigma_u$ , where  $\Sigma_c$  is a set of controllable events which can be enabled or disabled by external agents; and  $\Sigma_u$  is a set of uncontrollable events which cannot be disabled. We refer to such an external agent as a *supervisor*, which will formally define shortly.

**Definition 2.2.18.** Let  $L(\mathbf{S})$  be the language represented by DES S. We say S is a *supervisor* for G, if

- 1.  $L(\mathbf{S})$  is controllable with respect to  $\mathbf{G}$ , and

- 2.  $\overline{L_m(\mathbf{S}) \cap L_m(\mathbf{G})} = L(\mathbf{S}) \cap L(\mathbf{G})$

For convenience, we say **S** is *controllable* for **G** if  $L(\mathbf{S})$  is controllable with respect to **G**.

We can think of a supervisor  $\mathbf{S} = (X, \Sigma, \xi, x_o, X_m)$  as a state machine that tracks all the events generated by plant  $\mathbf{G}$ . Together with current state  $x \in X$  as source state, it takes each event as an input to its transition function  $\xi$ , then moves to the destination state  $x' \in X$ . Events in  $\mathbf{G}$  are only allowed to occur when the event is not disabled in  $\mathbf{S}$ . We refer to the closed loop behavior of the system as the behavior of our plant  $\mathbf{G}$  under the control of supervisor  $\mathbf{S}$ . This is typically represented as the meet of  $\mathbf{G}$  and  $\mathbf{S}$ . If we modeled the system only using the synchronous product, then this would be represented as  $\mathbf{G} || \mathbf{S}$ . As noted by Balemi in [2], controllable events tend to be events fully under the control of our supervisor's implementation. They may be a software function we call, an output we set to true, or a message we send. That means that we can make these events occur whenever we want. It is not unusual that a plant might be modeled such that these events are suppose to only occur under certain situations. This might be for flexibility (some implementations have these restrictions, for example) or to make the system easier to model or understand. However, the reality for some supervisor implementations is that these events could occur even when the plant said they cannot. We refer to such situations as *illegal transitions*. The requirement is formally defined in [2] as follows.

Definition 2.2.19. A plant G is *complete* for its supervisor S if

$$(\forall s \in L(\mathbf{G}) \cap L(\mathbf{S}))(\forall \sigma \in \Sigma_c) s \sigma \in L(\mathbf{S}) \implies s \sigma \in L(\mathbf{G})$$

The definition states that, at each state in plant  $\mathbf{G}$ , every controllable event enabled by supervisor  $\mathbf{S}$  must be accepted by  $\mathbf{G}$  as well. This condition can be seen as a dual to the definition of a supervisor  $\mathbf{S}$  being controllable for plant  $\mathbf{G}$ . This definition will be very useful for implementing DES supervisors, as it says that they do not require additional supplementary information from the plant to decide when a controllable event can occur and not violate the plant model.

## 2.3 Timed Discrete Event Systems

So far we have only discussed untimed DES. As we wish to use a richer modeling framework that includes timing requirements of our system, we will now discuss Timed DES (TDES) introduced by Brandin et al [5] [6].

TDES extends untimed DES theory by adding a new tick event, corresponding to the tick of a global clock. The event set of a TDES contains the tick event as well as other non-tick events called *activity* events ( $\Sigma_{act}$ ). The occurrence of a tick event provides us with a concept of time passing, allowing us to model upper and lower time bounds for the occurrence of activity events. A lower time bound for a given activity event can be modeled as requiring a certain number of tick events to first occur before the activity event is eligible. Once an activity event is eligible to occur in the TDES and the desired number of tick events have occurred, we can model an upper bound for the event by not allowing a tick event to occur until either the event has occurred, or another activity event has occur such that the first event is no longer eligible.

The addition of a tick event also allows us to introduce a new type of events called forcible events ( $\Sigma_{for}$ ), which we guarantee to occur and preempt the next clock tick. This means that now we cannot only prevent some events (referred to as prohibitable events ( $\Sigma_{hib}$ ) in TDES terminology) from occurring by disabling them, but we can also choose to have certain events occur before the next clock tick. As a convention, we sometimes refer to tick as  $\tau$  for brevity.

#### 2.3.1 Basic Structure

We formally define a TDES as the tuple

$$\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$$

where,

Q is the state set

- $\Sigma = \Sigma_{act} \cup \{\tau\}$  is the set of all events, including activity events and the tick event.

- $\delta: Q \times \Sigma \to Q$  is the (partial) transition function.

$q_0 \in Q$  is the initial state.

$Q_m \subseteq Q$  is the set of marked states.

For convenience, we extend  $\delta$  to function  $\delta: Q \times \Sigma^* \to Q$  in the same way as we did in the untimed DES definition.

### 2.3.2 Controllability and Supervision

Control action for timed DES is achieved in an analogous fashion as that of untimed DES, by disabling controllable events. As for untimed DES, we also partition our event set  $\Sigma$  into controllable and uncontrollable events. The set of controllable events is defined to be

$$\Sigma_c := \Sigma_{hib} \cup \{\tau\}$$

where  $\Sigma_{hib} \subseteq \Sigma_{act}$  the set of activity events that can disabled by an external agents. These event are referred to as prohibitable events to distinguish them from controllable events that include the tick event. As we will see when we define controllability in the TDES setting, we will use disabling the tick event by the supervisor to model forcing an event. A forcible event is an event in the system that we can make occur before the next clock tick, assuming it is not first preempted by another event. The set of *uncontrollable* events for **G** is then defined to be

$$\Sigma_u := \Sigma - \Sigma_c$$

In Section 2.2.3, we introduced Balemi's concept of completeness of a plant for a given supervisor. Unfortunately, that definition was given in terms of controllable events, which includes the tick event in TDES. As we are only concerned about the occurrence of activity events, we need to define a version of this definition for TDES. When discussing this concept, we will not specify whether or not we mean the timed or untimed version, as this will be clear by the context.

**Definition 2.3.1.** Let TDES **G** be a plant and TDES **S** be a supervisor. **G** is *TDES* complete for **S** if

$$(\forall s \in L(\mathbf{G}) \cap L(\mathbf{S}))(\forall \sigma \in \Sigma_{hib}) s \sigma \in L(\mathbf{S}) \implies s \sigma \in L(\mathbf{G})$$

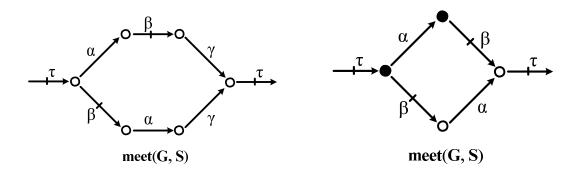

We now need to add a technical condition that we most enforce to ensure that our TDES does not allow the physically unrealistic situation where a tick event could be preempted indefinitely by the continued execution of an activity event loop within a given fixed unit time. Formally, a TDES is said to have an activity loop if it satisfies the following definition.

**Definition 2.3.2.** TDES  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  has an *activity loop* if

$$(\exists q \in Q)(\exists s \in \Sigma_{act}^+)\delta(q,s) = q$$

We thus require that a TDES be *activity loop free* (ALF). We can formalize the ALF concept as defined below.

**Definition 2.3.3.** TDES  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  is activity loop free if

$$(\forall q \in Q_{reach})(\forall s \in \Sigma_{act}^+)\delta(q, s) \neq q$$

We only look at states that are reachable (i.e. in  $Q_{reach}$ ), because we do not care about unreachable states as they do not contribute to the automaton's closed and marked behavior. These unreachable activity loops can be safely ignored. An example that fails the ALF property is shown in Figure 2.2 where the  $\alpha\beta$  loop could indefinitely preempt the tick event from occurring.

Figure 2.2: An Example Failing ALF Property

We will not require that supervisors be ALF, as they may contain self-loops that are not possible in the plant. We will instead require that the system's closed loop behavior (typically the meet of plant  $\mathbf{G}$  and supervisor  $\mathbf{S}$ ) be ALF.

For the FSM translation of individual supervisors in Section 4.2, we need a more specific definition as follows.

**Definition 2.3.4.** Let  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  be a TDES, and let  $\mathbf{G}'$  be  $\mathbf{G}$  with all activity event selfloops removed.  $\mathbf{G}$  is non-selfloop activity loop free if  $\mathbf{G}'$  is ALF.

Essentially, if we remove the selfloops of any activity events in the TDES, the rest of the TDES must be ALF. This will be a key definition that will allow us to translate the TDES to a Moore finite state machine.

The proposition below states that if individual DES are all ALF, it implies that the synchronous product of these DES is also ALF. This means that we can simply check the individual DES.

**Proposition 2.1.** For TDES  $\mathbf{G}_1 = (Q_1, \Sigma_1, \delta_1, q_{0,1}, Q_{m,1})$  and  $\mathbf{G}_2 = (Q_2, \Sigma_2, \delta_2, q_{0,2}, Q_{m,2})$ , if  $\mathbf{G}_1$  and  $\mathbf{G}_2$  are each ALF, then their synchronous product  $\mathbf{G} = \mathbf{G}_1 || \mathbf{G}_2$ , is ALF.

*Proof.* Let  $\mathbf{G}_1 = (Q_1, \Sigma_1, \delta_1, q_{0,1}, Q_{m,1})$  and  $\mathbf{G}_2 = (Q_2, \Sigma_2, \delta_2, q_{0,2}, Q_{m,2})$  be two TDES and let  $P_1 : \Sigma^* \to \Sigma_1^*$  and  $P_2 : \Sigma^* \to \Sigma_2^*$  be natural projections.

Define  $\Sigma_{act,i} = \Sigma_{act} \cap \Sigma_i, i = 1, 2.$

By ALF Definition 2.3.3, for i = 1, 2

$$(\forall q_i \in Q_{reach,i}) (\forall s_i \in \Sigma_{act,i}^+) \delta_i(q_i, s_i) \neq q_i \tag{*}$$

where  $Q_{reach,i}$  is the set of reachable states for  $\mathbf{G}_i$

Let  $\mathbf{G} = \mathbf{G}_1 || \mathbf{G}_2 = (Q, \Sigma, \delta, q_0, Q_m)$ Must show

$$(\forall q \in Q_{reach})(\forall s \in \Sigma_{act}^+)\delta(q, s) \neq q$$

We will use proof by contradiction. Assume

$$(\exists q \in Q_{reach})(\exists s' \in \Sigma_{act}^+)\delta(q, s') = q$$

Let  $q = (q_1, q_2) \in Q_{reach}$  be this state and let  $s' \in \Sigma_{act}^+$  such that  $\delta(q, s') = q$ .

We know that q is a reachable state if and only if  $q_1 \in Q_1$  and  $q_2 \in Q_2$  are reachable states in  $\mathbf{G}_1$  and  $\mathbf{G}_2$ , respectively, by Definition of the || operator. We thus have

$$\delta(q, s') = q \implies \delta((q_1, q_2), s') = (q_1, q_2)$$

$$\implies \delta((q_1, q_2), s') = (\delta_1(q_1, P_1(s')), \delta_2(q_2, P_2(s'))) \qquad \text{by Definition of } ||$$

This implies

$$\delta_1(q_1, P_1(s')) = q_1 \delta_2(q_2, P_2(s')) = q_2$$

As  $s' \in \Sigma_{act}^+$  we thus have  $s' \neq \epsilon$ . As  $\Sigma = \Sigma_1 \cup \Sigma_2$ , it follows that either  $P_1(s') \neq \epsilon$  or  $P_2(s') \neq \epsilon$  This implies that either  $\mathbf{G}_1$  or  $\mathbf{G}_2$  is not ALF, which contradicts(\*).

Therefore it must be that

$$(\forall q \in Q_{reach})(\forall s \in \Sigma_{act}^+)\delta(q, s) \neq q$$

The above proposition can be applied to two TDES combined using the meet operator as meet is a special case of the synchronous product.

We next present a proposition that says that to ensure the synchronous product is ALF, it is sufficient that only one of the two TDES is ALF, as long as the event set of the ALF TDES contains all of the events in the event set of the second TDES. It means that if plant is over  $\Sigma$  and the supervisor introduces no new events, then we can just check if the plant is ALF. As indicated by Proposition 2.1, we can check that the plant is ALF by checking if each individual plant component is ALF. Therefore an ALF algorithm does not have to check that the closed loop system is ALF, but can check that the event set of the plant is a superset of the supervisor's event set, then do an ALF check on each individual TDES that makes up the plant. If the check passes, then we are done. Otherwise, we do an ALF check on the entire system.

**Proposition 2.2.** Let  $\mathbf{G}_1 = (Q_1, \Sigma_1, \delta_1, q_{o,1}, Q_{m,1})$  and  $\mathbf{G}_2 = (Q_2, \Sigma_2, \delta_2, q_{o,2}, Q_{m,2})$  be two TDES. If  $\mathbf{G}_1$  is ALF and  $\Sigma_1 \supseteq \Sigma_2$ , then  $\mathbf{G}_1 || \mathbf{G}_2$  is also ALF.

Proof. Assume  $\mathbf{G}_1$  is ALF and  $\Sigma_1 \supseteq \Sigma_2$ . (1) Let  $\mathbf{G} = \mathbf{G}_1 || \mathbf{G}_2 = (Q, \Sigma, \delta, q_o, Q_m)$  with  $\Sigma = \Sigma_1 \cup \Sigma_2$  and  $P_i : \Sigma^* \to \Sigma_i^*$  for i = 1, 2. Must show  $\mathbf{G}$  is ALF.

We will do so by proof of contradiction.

Assume  $\mathbf{G}$  is not ALF, then

$$(\exists q \in Q_{reach})(\exists s' \in \Sigma^+ act)\delta(q, s') = q$$

Let  $q = (q_1, q_2) \in Q_{reach}$ , and  $s' \in \Sigma_{act}^+$  such that  $\delta(q, s') = q$ . (2)

We first note that q is reachable in  $\mathbf{G}$ , which implies  $q_1$  is reachable in  $\mathbf{G}_1$  and  $q_2$  is reachable in  $\mathbf{G}_2$ .

We next note that as  $\Sigma_1 \supseteq \Sigma_2$ , we have  $\Sigma = \Sigma_1 \cup \Sigma_2 = \Sigma_1$ . This implies that  $P_1^{-1}L(\mathbf{G}_1) = L(\mathbf{G}_1).$  (3)

From (2), we have

=

$$\delta(q, s') = q \implies \delta((q_1, q_2), s') = (q_1, q_2)$$

$$\implies \qquad \delta_1(q_1, P_1(s')) = q_1$$

$$\implies \qquad \delta_1(q_1, s') = q_1 \qquad \text{by (3)}$$

This contradicts (1) as it implies  $\mathbf{G}_1$  is not ALF.

We thus conclude that **G** must be ALF.

We are also want to make sure that the plant is not modeled in such a way that our closed loop system could reach a state where no more tick events are possible, as this "stopping the clock" would be physically unrealistic. To help prevent this, we will require that our plant TDES have *proper time behavior*, as defined by Kai Wong et al. [28].

**Definition 2.3.5.** TDES **G** has a *proper time behavior* if

$$(\forall s \in L(\mathbf{G})) \operatorname{Elig}_{L(\mathbf{G})}(s) \cap \Sigma_u = \emptyset \implies \tau \in \operatorname{Elig}_{L(\mathbf{G})}(s)$$

This definition can be rewritten as

$$(\forall q \in Q_{reach})(\exists \sigma \in \Sigma_u \cup \{\tau\})\delta(q, \sigma)!$$

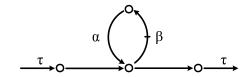

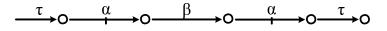

In other words, this TDES must guarantee that at all of its reachable states, either a tick event or an uncontrollable event must be possible. This serves two purposes. Combined with TDES **G** being ALF and having a finite state space, this ensures that we call always reach a state where a tick is possible after at most a finite number of activity events. We prove this shortly in Proposition 2.3. This condition will also ensure we do not stop the clock when we combine our plant with a controllable supervisor. An example that fails the proper time behavior property is shown in Figure 2.3 where after the first tick event, neither an uncontrollable event or a tick are possible, only the prohibitable event  $\beta$ .

$\xrightarrow{\tau} \circ \xrightarrow{\beta} \circ \xrightarrow{\alpha} \circ \xrightarrow{\tau} \circ$

Figure 2.3: An Example Failing the Proper Time Behavior Property

Consider the case where we have a reachable state where tick was ineligible, but only controllable events were possible. If the supervisor disabled these controllable events, there would now be no events possible at all. Proper time behavior ensures that if tick was not possible at this state in the plant, there would be an uncontrollable event possible, even if all the controllable events were disabled. The restriction of proper time behavior applies only to plant TDES. It does not apply to supervisor TDES or the meet of the plant and supervisor (i.e. the closed loop behavior of the system). If a TDES G has a finite state space, is activity loop free and has proper time behavior, then we expect that at any reachable state, we can always do a tick event after at most a finite number of activity events. In other words, we will never "stop the clock." The following proposition shows that this is indeed the case.

**Proposition 2.3.** If a TDES  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  has a finite statespace, is activity loop free and has proper time behavior, then

$$(\forall q \in Q_{reach})(\exists s \in \Sigma^*)\delta(q, s\tau)!$$

where  $Q_{reach}$  is the set of reachable states.

*Proof.* Assume that  $\mathbf{G}$  has a finite statespace, is activity loop free, and has proper time behavior

Let  $q \in Q_{reach}$ .

Must show implies  $(\exists s \in \Sigma^*) \delta(q, s\tau)!$