# Implementation of Sampled-Data Supervisory Control

By Abubaker Hamid, M.Sc

A Thesis Submitted to the School of Graduate Studies in partial fulfilment of the requirements for the degree of

Master of Science Department of Computing and Software McMaster University

© Copyright by Abubaker Hamid, June 17, 2014

## MASTER OF SCIENCE(2014) (Computer Science)

McMaster University Hamilton, Ontario

| TITLE:      | Implementation of Sampled-data Supervisory Control               |

|-------------|------------------------------------------------------------------|

| AUTHOR:     | Abubaker Hamid, M.Sc(Sudan University of Science and Technology) |

| SUPERVISOR: | Prof. Ryan J. Leduc                                              |

NUMBER OF PAGES: i, 183

# Dedication

To my son, Abdul Rahman Abubaker Mahmoud.

## Abstract

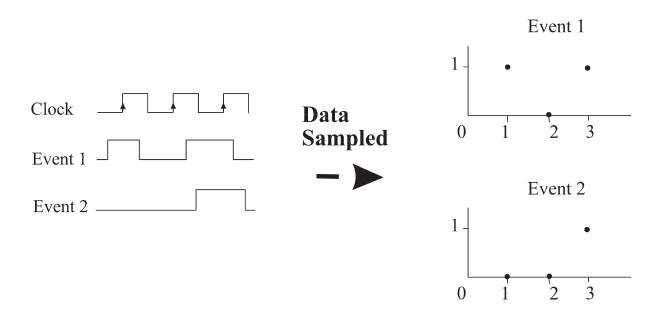

This thesis focuses on the issues related to the implementation of theoretical timed discrete-event systems (TDES) supervisors. In particular, we examine issues related to implementing TDES as sampled-data (SD) controllers, which were introduced by Wang and Leduc. [18], [21], and [22]. An SD controller is driven by a periodic clock and sees the system as a series of inputs and outputs. On each clock edge (*tick* event), it samples its inputs, changes state, and updates its outputs.

We first introduce the sampled-data setting from Wang, and then define the sampled-data properties he identified, including the SD controllability property. We then introduce Wang's formal representation of an SD controller as a Moore synchronous finite state machine (FSM). We then discuss Wang's modular and centralized translation method.

We next introduced new modular results for the SD controllability point 3.1, SD controllability point 3.2, SD controllability point 4, activity loop free and S-singular prohibitable behaviour that allow one to verify the properties using only a portion of the system, instead of having to construct the entire system model. This should allow faster verification times as well as allow larger systems to be verified. As a part of this work, we broke down into individual algorithms one of the large algorithms from Wang that checked multiple properties at once. We can now check each property individually. We then introduce for the first time algorithms to verify Wang's CS Deterministic and non self-loop ALF properties.

The remainder of the thesis focuses on developing algorithms and software to automatically convert a TDES first into an FSM, and then into a VERILOG module. VERILOG is a hardware description language which allows our FSM to be compiled and implemented on digital logic devices such as an FPGA.

We then tested our method by modelling a simple door locking system as TDES, checking that the system satisfies the required sampled-data properties, and then translating the result into VERILOG. The above algorithms and methods have all been implemented as a part of the graphical DES research tool, DESpot.

## Acknowledgements

Thank you God, in the beginning and in the end, for giving me the power to continue and finish this work. I would like to thank Professor Ryan J. Leduc, who patiently guided me through the dark corridors of the discrete-events systems area, enlightening these corridors and providing me with enough resources for the research. I would like to thank Yu Wang for the clarity and organization of his thesis, about the areas that needed to be extended and implemented.

## Notation and Abbreviations

In this thesis we will use the following notations and abbreviations

**DES**: Discrete event systems.

- **TDES**: Timed discrete event systems.

- ${\bf SD}:$  Sampled Data.

- **FSM**: Finite State Machine.

VERILOG: IEEE: 1364-2005 - Hardware definition language.

ALF: Activity Loop Free.

NSL ALF: Non-self-loop Activity Loop Free.

**SPB**: Singular prohibitable behaviour.

**SSPB**: S-Singular prohibitable behaviour.

CS Deterministic: Concurrent string deterministic.

**PTB**: Proper time behaviour.

0. Notation and Abbreviations

# Contents

| D             | edica      | ion                                                                | iii                                                     |

|---------------|------------|--------------------------------------------------------------------|---------------------------------------------------------|

| $\mathbf{A}$  | bstra      | t                                                                  | $\mathbf{v}$                                            |

| A             | cknov      | ledgements                                                         | vii                                                     |

| N             | otati      | n and Abbreviations                                                | ix                                                      |

| Co            | onter      | s                                                                  | xi                                                      |

| $\mathbf{Li}$ | st of      | Figures                                                            | xv                                                      |

| 1<br>2        | 1.1<br>1.2 | duction         Previous Work                                      | <b>1</b><br>1<br>3<br><b>5</b><br>5<br>5<br>6<br>8<br>8 |

|               |            | 2.2.1TDES2.2.2Synchronization and Product TDES2.2.3TDES Properties | 8<br>12<br>14                                           |

| 3             |            |                                                                    | 19                                                      |

|               | 3.1        |                                                                    | 19                                                      |

|               | 3.2        |                                                                    | 21                                                      |

|               | 3.3        | SD Controllable Languages                                          | 25                                                      |

| 4.2       Formal Model       31         4.3       Translation Method Introduction       33         4.4       Event Mapping Functions       37         4.5       Centralized Translation Method       38         4.6       Output Equivalence       39         4.7       Modular Translation Method       40         4.8       FSM as VERILOG Module       42         4.9       Field-Programmable Gate Array       43         5       Modular Verification of Sampled-Data Properties       45         5.1       Introduction to Previous Work       45         5.2       ALF Modularity       46         5.3       SPB and SSPB Modularity       47         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iii.2 Modularity       55         5.4.3       SD-Cont-iii.2 Modularity       55         5.4.3       SD-Cont-iii.2 Modularity       55         6.4       Algorithmic Improvements       59         6.2.1       State Predicates       60                                                                                                                    | 4 | Mo             | ore Finite State Machines (FSM) and VERILOG              | <b>31</b> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|----------------------------------------------------------|-----------|

| 4.3Translation Method Introduction334.4Event Mapping Functions374.5Centralized Translation Method384.6Output Equivalence394.7Modular Translation Method404.8FSM as VERILOG Module424.9Field-Programmable Gate Array435Modular Verification of Sampled-Data Properties455.1Introduction to Previous Work455.2ALF Modularity465.3SPB and SSPB Modularity475.3.1SPB implies SSPB475.3.2SPB Modularity505.4.1SD-Cont-iii.1 Modularity505.4.3SD-Cont-iii.2 Modularity555.4.3SD-Cont-iii.2 Modularity556Algorithmic Improvements596.1Introduction596.2Predicate Verification Preliminaries596.3Previous Approach626.4Modular Verification Algorithm676.5Modular Verification Algorithm676.6System ALF Algorithm806.7Non-selfloop ALF Algorithm836.8SD Controllability, SSPB and CS Deterministic Algorithms846.8.2AnalyseSampledState Algorithm887VERILOG Translation957.1Introduction957.2TDES to FSM95                                                                                                                                                                                                                                                                                                                                                   |   | 4.1            | Moore FSM                                                | 31        |

| 4.4       Event Mapping Functions       37         4.5       Centralized Translation Method       38         4.6       Output Equivalence       39         4.7       Modular Translation Method       40         4.8       FSM as VERILOG Module       42         4.9       Field-Programmable Gate Array       43         5       Modular Verification of Sampled-Data Properties       45         5.1       Introduction to Previous Work       45         5.2       ALF Modularity       46         5.3       SPB and SSPB Modularity       47         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iw Modularity       50         5.4.3       SD-Cont-iw Modularity       50         6.4       Algorithmic Improvements       59         6.2       Predicate Verification Preliminaries       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62                                                                                                                  |   | 4.2            | Formal Model                                             | 31        |

| 4.5       Centralized Translation Method       38         4.6       Output Equivalence       39         4.7       Modular Translation Method       40         4.8       FSM as VERILOG Module       42         4.9       Field-Programmable Gate Array       43         5       Modular Verification of Sampled-Data Properties       45         5.1       Introduction to Previous Work       45         5.2       ALF Modularity       46         5.3       SPB and SSPB Modularity       47         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iii.2 Modularity       55         5.4.3       SD-Cont-iw Modularity       55         6       Algorithmic Improvements       59         6.1       Introduction       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5 <td></td> <td>4.3</td> <td>Translation Method Introduction</td> <td>33</td>                                          |   | 4.3            | Translation Method Introduction                          | 33        |

| 4.5       Centralized Translation Method       38         4.6       Output Equivalence       39         4.7       Modular Translation Method       40         4.8       FSM as VERILOG Module       42         4.9       Field-Programmable Gate Array       43         5       Modular Verification of Sampled-Data Properties       45         5.1       Introduction to Previous Work       45         5.2       ALF Modularity       46         5.3       SPB and SSPB Modularity       47         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iii.2 Modularity       55         5.4.3       SD-Cont-iw Modularity       55         6       Algorithmic Improvements       59         6.1       Introduction       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5 <th></th> <th>4.4</th> <th>Event Mapping Functions</th> <th>37</th>                                                  |   | 4.4            | Event Mapping Functions                                  | 37        |

| 4.7       Modular Translation Method       40         4.8       FSM as VERILOG Module       42         4.9       Field-Programmable Gate Array       43         5       Modular Verification of Sampled-Data Properties       45         5.1       Introduction to Previous Work       45         5.2       ALF Modularity       46         5.3       SPB and SSPB Modularity       47         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iw Modularity       55         5.4.3       SD-Cont-iw Modularity       55         6       Algorithmic Improvements       59         6.1       Introduction       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5       Modular Version of VerifySub       78         6.6                                                                                                                             |   | 4.5            |                                                          | 38        |

| 4.7       Modular Translation Method       40         4.8       FSM as VERILOG Module       42         4.9       Field-Programmable Gate Array       43         5       Modular Verification of Sampled-Data Properties       45         5.1       Introduction to Previous Work       45         5.2       ALF Modularity       46         5.3       SPB and SSPB Modularity       47         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iw Modularity       55         5.4.3       SD-Cont-iw Modularity       55         6       Algorithmic Improvements       59         6.1       Introduction       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5       Modular Version of VerifySub       78         6.6                                                                                                                             |   | 4.6            | Output Equivalence                                       | 39        |

| 4.8       FSM as VERILOG Module       42         4.9       Field-Programmable Gate Array       43         5       Modular Verification of Sampled-Data Properties       45         5.1       Introduction to Previous Work       45         5.2       ALF Modularity       46         5.3       SPB and SSPB Modularity       47         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iii.2 Modularity       55         5.4.3       SD-Cont-iv Modularity       55         6       Algorithmic Improvements       59         6.1       Introduction       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5       Modular Verification Algorithm       67         6.6       System ALF Algorithm       83         6.7       Non-selfloop ALF Algorithm       83         6.8 </th <th></th> <th>4.7</th> <th></th> <th>40</th>                                                                  |   | 4.7            |                                                          | 40        |

| 4.9       Field-Programmable Gate Array       43         5       Modular Verification of Sampled-Data Properties       45         5.1       Introduction to Previous Work       45         5.2       ALF Modularity       46         5.3       SPB and SSPB Modularity       46         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iii.2 Modularity       50         5.4.3       SD-Cont-iv Modularity       55         6       Algorithmic Improvements       59         6.1       Introduction       59         6.2       Predicate Verification Preliminaries       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5       Modular Verification Algorithm       67         6.5       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83                                                                                                                 |   | 4.8            |                                                          | 42        |

| 5.1       Introduction to Previous Work       45         5.2       ALF Modularity       46         5.3       SPB and SSPB Modularity       47         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iii.2 Modularity       55         5.4.3       SD-Cont-iw Modularity       55         6       Algorithmic Improvements       59         6.1       Introduction       59         6.2.1       State Predicates       60         6.2.2       Predicate Verification Preliminaries       59         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5       Modular Verification Algorithm       67         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.2       AnalyseSampledState Algorithm       86         6.8.2       AnalyseSampledState Algorithm       86 <th></th> <th></th> <th></th> <th>43</th>                                                 |   |                |                                                          | 43        |

| 5.1       Introduction to Previous Work       45         5.2       ALF Modularity       46         5.3       SPB and SSPB Modularity       47         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iii.2 Modularity       55         5.4.3       SD-Cont-iw Modularity       55         6       Algorithmic Improvements       59         6.1       Introduction       59         6.2.1       State Predicates       60         6.2.2       Predicate Verification Preliminaries       59         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5       Modular Verification Algorithm       67         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.2       AnalyseSampledState Algorithm       86         6.8.2       AnalyseSampledState Algorithm       86 <th>5</th> <th>Mo</th> <th>dular Verification of Sampled-Data Properties</th> <th>45</th> | 5 | Mo             | dular Verification of Sampled-Data Properties            | 45        |

| 5.2       ALF Modularity       46         5.3       SPB and SSPB Modularity       47         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iii.2 Modularity       50         5.4.3       SD-Cont-iw Modularity       55         5.4.3       SD-Cont-iv Modularity       55         6       Algorithmic Improvements       59         6.1       Introduction       59         6.2       Predicate Verification Preliminaries       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5       Modular Version of VerifySub       78         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.2       AnalyseSampledState Algorithm       86                                                                                                            | 0 |                |                                                          |           |

| 5.3       SPB and SSPB Modularity       47         5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iii.2 Modularity       50         5.4.3       SD-Cont-iii.2 Modularity       55         5.4.3       SD-Cont-iw Modularity       55         6       Algorithmic Improvements       59         6.1       Introduction       59         6.2       Predicate Verification Preliminaries       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       62         6.4       Modular Verification Algorithm       62         6.5       Modular Version of VerifySub       78         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       80         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm                                                                                               |   | -              |                                                          | -         |

| 5.3.1       SPB implies SSPB       47         5.3.2       SPB Modularity       48         5.4       SD Controllability Modularity       50         5.4.1       SD-Cont-iii.1 Modularity       50         5.4.2       SD-Cont-iii.2 Modularity       55         5.4.3       SD-Cont-iv Modularity       55         6       Algorithmic Improvements       59         6.1       Introduction       59         6.2       Predicate Verification Preliminaries       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5       Modular Verification Algorithm       67         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95                                                                                                       |   |                | *                                                        | -         |

| 5.3.2SPB Modularity485.4SD Controllability Modularity505.4.1SD-Cont-iii.1 Modularity505.4.2SD-Cont-iii.2 Modularity555.4.3SD-Cont-iv Modularity556Algorithmic Improvements596.1Introduction596.2Predicate Verification Preliminaries596.2.1State Predicates606.2.2Predicate Transformers616.3Previous Approach626.4Modular Verification Algorithm676.5Modular Verification Algorithm676.6System ALF Algorithm806.7Non-selfloop ALF Algorithm836.8SD Controllability, SSPB and CS Deterministic Algorithms846.8.1CheckSDCont_SSPB_CSDet Algorithm866.8.2AnalyseSampledState Algorithm887VERILOG Translation957.1Introduction957.2TDES to FSM95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 0.0            |                                                          | -         |

| 5.4SD Controllability Modularity505.4.1SD-Cont-iii.1 Modularity505.4.2SD-Cont-iii.2 Modularity555.4.3SD-Cont-iv Modularity556Algorithmic Improvements596.1Introduction596.2Predicate Verification Preliminaries596.2.1State Predicates606.2.2Predicate Transformers616.3Previous Approach626.4Modular Verification Algorithm676.5Modular Verification Algorithm676.6System ALF Algorithm806.7Non-selfloop ALF Algorithm836.8SD Controllability, SSPB and CS Deterministic Algorithms846.8.1CheckSDCont_SSPB_CSDet Algorithm866.8.2AnalyseSampledState Algorithm887VERILOG Translation957.1Introduction957.2TDES to FSM95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                |                                                          | -         |

| 5.4.1       SD-Cont-iii.1       Modularity       50         5.4.2       SD-Cont-iii.2       Modularity       55         5.4.3       SD-Cont-iv       Modularity       55         6       Algorithmic Improvements       59       6.1       Introduction       59         6.1       Introduction       59       6.2       Predicate Verification Preliminaries       59         6.2.1       State Predicates       59       6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61       63       61         6.3       Previous Approach       62       64         6.4       Modular Verification Algorithm       67       65         6.5       Modular Verification Algorithm       67       67         6.5       Modular Version of VerifySub       78       78         6.6       System ALF Algorithm       83       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.2       TDES to FSM       95                                                                                        |   | 5 /            |                                                          |           |

| 5.4.2SD-Cont-iii.2 Modularity555.4.3SD-Cont-iv Modularity556Algorithmic Improvements596.1Introduction596.2Predicate Verification Preliminaries596.2.1State Predicates606.2.2Predicate Transformers616.3Previous Approach626.4Modular Verification Algorithm676.5Modular Verification Algorithm786.6System ALF Algorithm806.7Non-selfloop ALF Algorithm836.8SD Controllability, SSPB and CS Deterministic Algorithms846.8.1CheckSDCont_SSPB_CSDet Algorithm866.8.2AnalyseSampledState Algorithm857VERILOG Translation957.1Introduction957.2TDES to FSM95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 0.4            |                                                          |           |

| 5.4.3SD-Cont-iv Modularity556Algorithmic Improvements596.1Introduction596.2Predicate Verification Preliminaries596.2.1State Predicates606.2.2Predicate Transformers616.3Previous Approach626.4Modular Verification Algorithm676.5Modular Version of VerifySub786.6System ALF Algorithm806.7Non-selfloop ALF Algorithm836.8SD Controllability, SSPB and CS Deterministic Algorithms846.8.1CheckSDCont_SSPB_CSDet Algorithm866.8.2AnalyseSampledState Algorithm887VERILOG Translation957.1Introduction957.2TDES to FSM95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                | 5                                                        |           |

| 6       Algorithmic Improvements       59         6.1       Introduction       59         6.2       Predicate Verification Preliminaries       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5       Modular Verification Algorithm       67         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                  |   |                |                                                          |           |

| 6.1       Introduction       59         6.2       Predicate Verification Preliminaries       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       62         6.4       Modular Verification Algorithm       67         6.5       Modular Version of VerifySub       78         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                            |   |                | 5.4.5 SD-Cont-IV Modularity                              | 55        |

| 6.2       Predicate Verification Preliminaries       59         6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       62         6.5       Modular Verification Algorithm       67         6.5       Modular Version of VerifySub       78         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       80         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                    | 6 | $\mathbf{Alg}$ | -                                                        | 59        |

| 6.2.1       State Predicates       60         6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       62         6.4       Modular Verification Algorithm       67         6.5       Modular Version of VerifySub       78         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       85         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 6.1            |                                                          | 59        |

| 6.2.2       Predicate Transformers       61         6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5       Modular Version of VerifySub       78         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | 6.2            |                                                          | 59        |

| 6.3       Previous Approach       62         6.4       Modular Verification Algorithm       67         6.5       Modular Version of VerifySub       78         6.6       System ALF Algorithm       78         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       85         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                | 6.2.1 State Predicates                                   | 60        |

| 6.4       Modular Verification Algorithm       67         6.5       Modular Version of VerifySub       78         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       80         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       83         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                | 6.2.2 Predicate Transformers                             | 61        |

| 6.5       Modular Version of VerifySub       78         6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 6.3            | Previous Approach                                        | 62        |

| 6.6       System ALF Algorithm       80         6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 6.4            | Modular Verification Algorithm                           | 67        |

| 6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 6.5            | Modular Version of VerifySub                             | 78        |

| 6.7       Non-selfloop ALF Algorithm       83         6.8       SD Controllability, SSPB and CS Deterministic Algorithms       84         6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 6.6            | System ALF Algorithm                                     | 80        |

| 6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 6.7            | Non-selfloop ALF Algorithm                               | 83        |

| 6.8.1       CheckSDCont_SSPB_CSDet Algorithm       86         6.8.2       AnalyseSampledState Algorithm       88         7       VERILOG Translation       95         7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 6.8            | SD Controllability, SSPB and CS Deterministic Algorithms | 84        |

| 6.8.2AnalyseSampledState Algorithm887VERILOG Translation957.1Introduction957.2TDES to FSM95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                |                                                          | 86        |

| 7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                | 0                                                        | 88        |

| 7.1       Introduction       95         7.2       TDES to FSM       95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7 | VE             | RILOG Translation                                        | 95        |

| 7.2 TDES to FSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • |                |                                                          |           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | -              |                                                          |           |

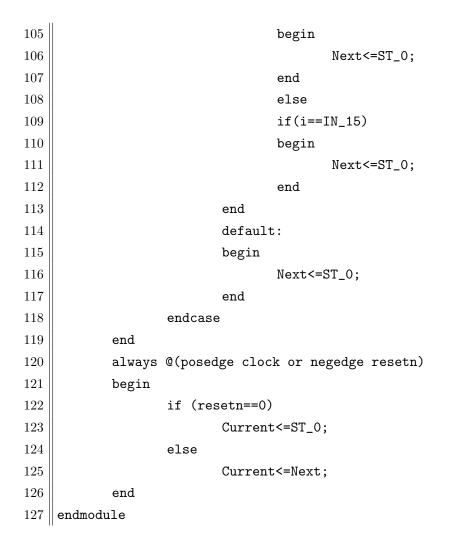

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 7.2            | FSM to VERILOG                                           | 100       |

|    | 7.4   | Centeral FSM for SD Controllers 10                                                                                                              | )4         |

|----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|    | 7.5   | Central Module for SD Controllers 10                                                                                                            | )6         |

|    | 7.6   | Translation Algorithms                                                                                                                          | )9         |

|    |       | 7.6.1 write $FSM()$ Algorithm                                                                                                                   | 5          |

|    |       | 7.6.2 writeHFSM() Algorithm $\dots \dots \dots$ | 7          |

|    |       | 7.6.3 mainVERILOG() Algorithm                                                                                                                   | 21         |

|    |       | 7.6.4 writeVERILOG() Algorithm                                                                                                                  | 26         |

|    |       | 7.6.5 mainFSM() Algorithm $\ldots \ldots 13$                              | 35         |

|    | 7.7   | Removing Redundant Transitions                                                                                                                  | \$7        |

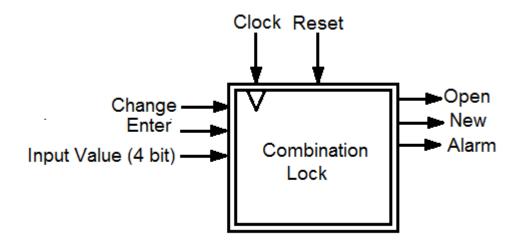

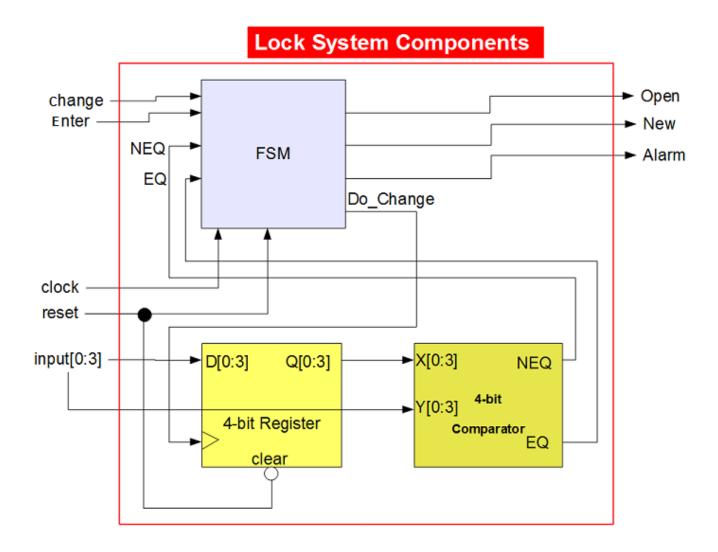

| 8  | Loc   | k System Example 13                                                                                                                             | 9          |

|    | 8.1   | Problem Description                                                                                                                             | 39         |

|    |       | 8.1.1 System Components                                                                                                                         | 1          |

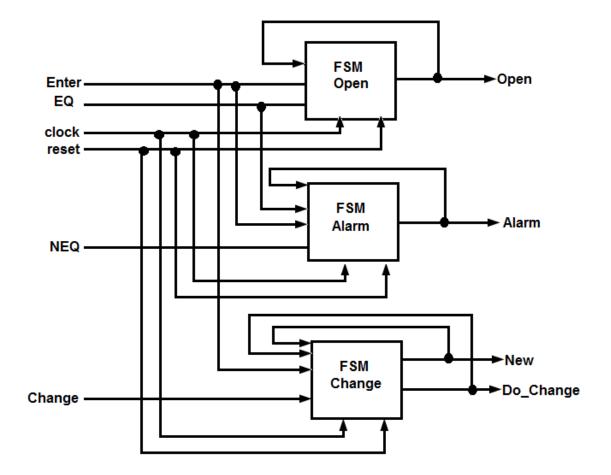

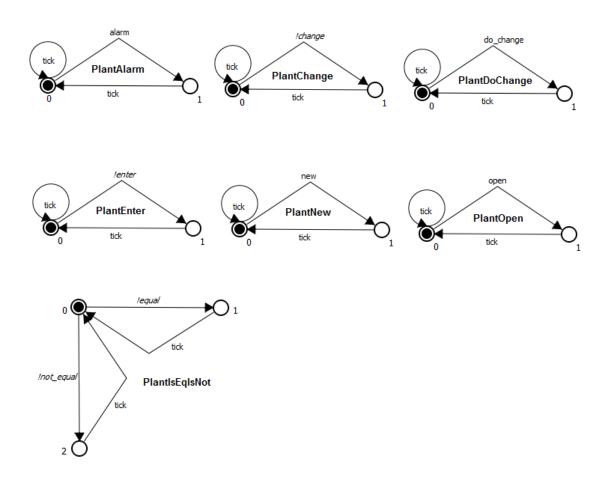

|    | 8.2   | Components Design                                                                                                                               | 13         |

|    |       | 8.2.1 Signal Outputs and Transitions                                                                                                            | 6          |

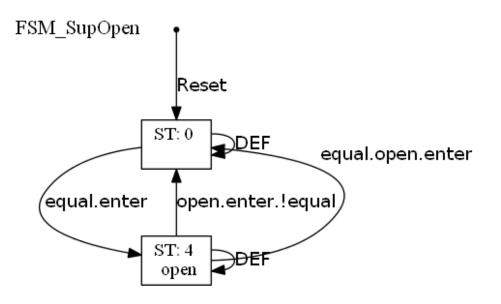

|    |       | 8.2.2 Supervisor SupOpen                                                                                                                        | 8          |

|    |       | 8.2.3 Supervisor SupChange                                                                                                                      | 52         |

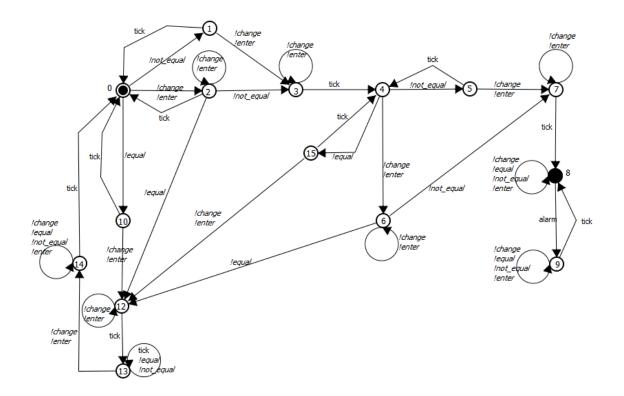

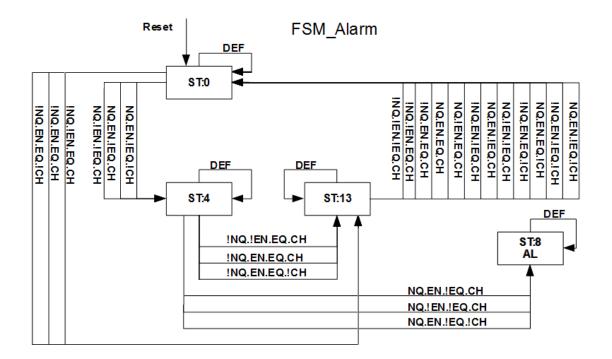

|    |       | 8.2.4 Supervisor SupAlarm                                                                                                                       | 59         |

|    |       | 8.2.5 The Main Controller FSM                                                                                                                   | 59         |

|    | 8.3   | Performance Results                                                                                                                             | '2         |

|    | 8.4   | Other Projects Performance Results                                                                                                              | <b>'</b> 4 |

|    |       | 8.4.1 Flexible Manufacturing System                                                                                                             | <b>'</b> 4 |

|    |       | 8.4.2 Test Station of Manufacturing System                                                                                                      | '5         |

| 9  | Cor   | nclusion 17                                                                                                                                     | 7          |

| -  | 9.1   | Conclusion                                                                                                                                      | 77         |

|    | 9.2   | Future Work                                                                                                                                     | '9         |

| Bi | bliog | graphy 18                                                                                                                                       | 1          |

# List of Figures

| 2.1  | ADAM Language Automata                                                 | 7   |

|------|------------------------------------------------------------------------|-----|

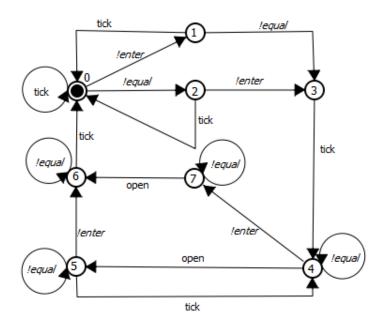

| 2.2  | An Example TDES                                                        | 11  |

| 2.3  | An Example Failing ALF Property, from Wang [21]                        | 15  |

| 2.4  | An Example Failing the Proper Time Behavior Property, from Wang [21]   | 17  |

|      |                                                                        |     |

| 3.1  | Sampling Data Global <i>tick</i>                                       | 20  |

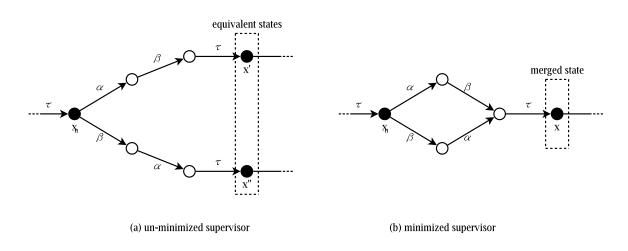

| 3.2  | Nonminimal Example                                                     | 24  |

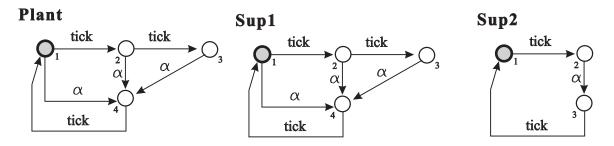

| 3.3  | An Example for <b>Point ii</b> , from Leduc et al [18]                 | 27  |

| 3.4  | An Example for <b>Point iii.1</b> , from Leduc et al [18]              | 29  |

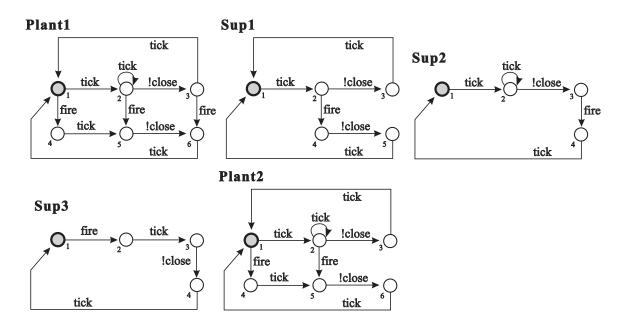

| 3.5  | An Example for <b>Point iii.2 and Point iv</b> , from Leduc et al [18] | 30  |

|      |                                                                        |     |

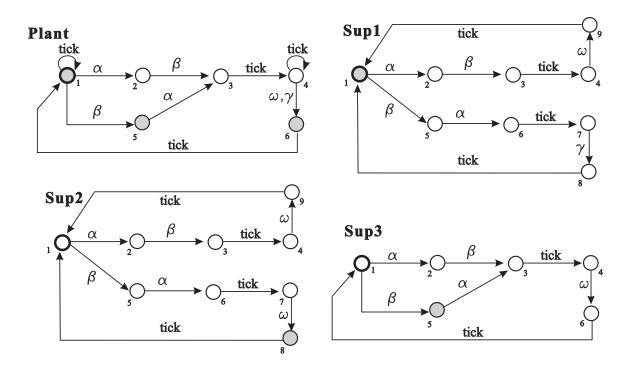

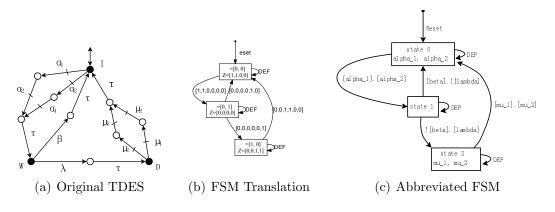

| 4.1  | FSM Translation Example                                                | 33  |

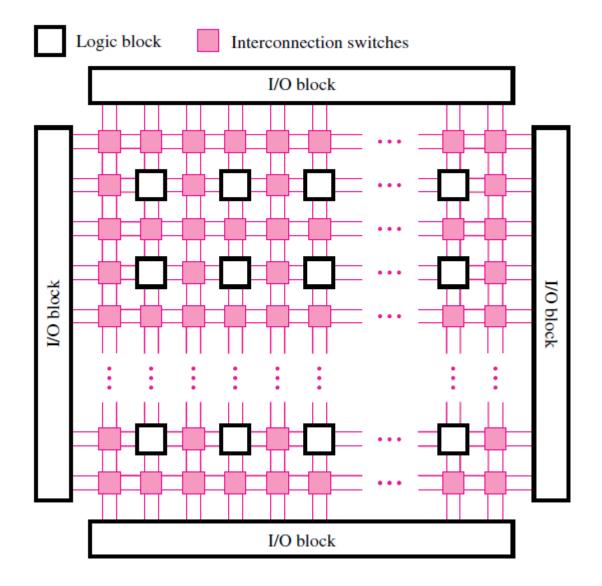

| 4.2  | General Structure of FPGA, [9]                                         | 44  |

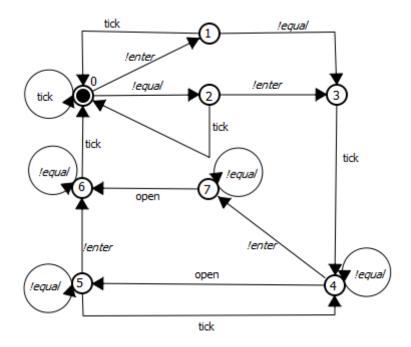

| 7.1  | Supervisor SupOpen                                                     | 97  |

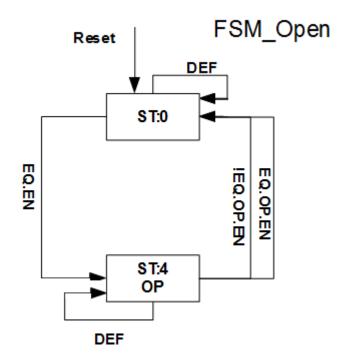

| 7.2  | FSM of Supervisor <b>SupOpen</b>                                       | 98  |

| 7.3  |                                                                        | 111 |

| 7.4  |                                                                        | 112 |

|      |                                                                        |     |

| 8.1  | J 0                                                                    | 140 |

| 8.2  | v 0                                                                    | 142 |

| 8.3  | FSM Detailed Sub-Modules                                               | 143 |

| 8.4  | Lock System Plants Components                                          | 146 |

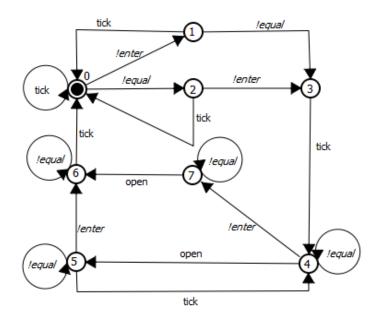

| 8.5  | Supervisor SupOpen                                                     | 148 |

| 8.6  |                                                                        | 149 |

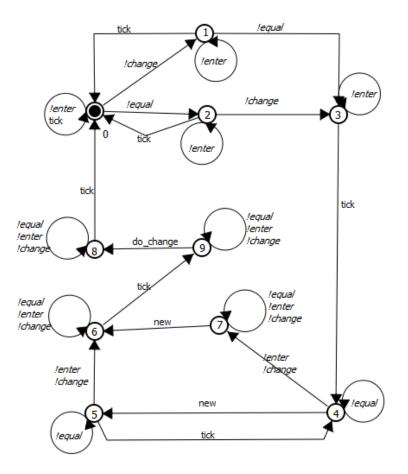

| 8.7  | Supervisor SupChange                                                   | 153 |

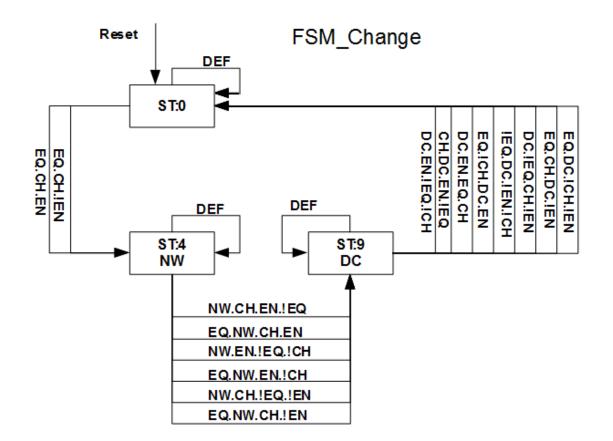

| 8.8  |                                                                        | 154 |

| 8.9  |                                                                        | 160 |

| 8.10 |                                                                        | 161 |

|      |                                                                        |     |

# Chapter 1

## Introduction

## 1.1 Previous Work

Since ancient times such as 300 BC in Greece, man has been fond of controlling natural aspects around him. He started this control spree by inventing the clock (Time monitoring machine) with combined effort between Arabs and Greeks. The spree started by creating machines to track aspects around man, then continued to cover instruments for tracking the moon and other planet's motion, the direction of air flow, the prediction of seasons and most importantly, the compass.

Systems control theory had been there for a long time in the beginning of the steam engine era (18th century). However, implementing these theories in a practical methodology had only taken serious shape in the last few decades, with the introduction of a vast quantity of hardware controllers such as PLC [23], and the sophistication of Hardware Description Languages (HDL) such as VHDL [10], VERILOG [9].

The area of discrete event systems (DES) had been a target for serious theoretical studies, creating a base for a linguistic approach, that helps in analysing and applying properties, such as nonblocking, controllability. These serious studies can be found in [16] and [26]. The linguistic approach is inspired by looking at systems as languages and model them in terms of sentences and words.

A solid approach to implement supervisors as Sampled-data controllers was led by Leduc and Wang [18] [21] [22]. They introduced the concept of Sampled-data controllers as well as new properties such as SD controllability to make sure the behaviour of the controllers was closer to the theoretical model. This method focuses on timed DES [8] and [7]. We will be extending Wang's work.

An earlier attempt to implement untimed supervisors is the the implementation of Leduc in [14] and [15] of an finite state machine (FSM) version named Clocked Moore Synchronous State Machine (CMSSM) on a programmable logic controller (PLC). A test bed system was implemented which contains 29 DES supervisors. The system's synchronous product was order of  $10^{16}$  states, worst case estimate. For additional examples of early works, see [18].

As for the modular verification we implemented in this thesis, it was inspired by the modular incremental verification for controllability by Malik et al [5]. This was a new approach, to verify systems and do synthesis, based on subsystem verification and combined use of counterexamples and heuristics to identify suitable subsystems incrementally. We also build upon the work by Wang [21] and Baloch [3].

There were plenty of good efforts in implementing system controls in variety of ways. Julien Provost, Jean-Marc Roussel and Jean-Marc Faure [13] had implemented a system that evaluates that the specifications of a system is testable, then implemented this using a Mealy FSM and PLC.

Aside from systems control, OMNET++ [20] is a huge work done in C++. OM-NET++ is an open source library for C++ development that helps a lot in the area of discrete event systems' simulation. It has module building blocks for the system and uses messaging to enable the sub modules to communicate with each other. It is very useful in simulation, particularly network simulation and telecommunication systems simulation.

## 1.2 Objectives

Our objective in this work has two focuses. The first is to enhance the performance of the current SD controllability verification automation in DESpot, by enhancing the algorithms implemented so far. We do this by either splitting algorithms that are combined in function such as SSPB, SD controllability and CS deterministic, or by enhancing the code of the BDD-based algorithms themselves.

We also have to build new algorithms for the properties such as non-self loop activity free loop (NSL ALF), CS deterministic and translation algorithms that translates supervisors first into intermediate Moore FSM modules, and then then into VER-ILOG modules.

Our second focus is the implementation of sampled data supervisors. All the properties and theories of sampled data supervisory control is useless if not converted into a practical hardware or software implementation. In this work, we will translate traditional TDES supervisors into real VERILOG modules that will be programmed into digital hardware such as FPGA, to create concrete implementation of our supervisors. Please see Chapter 4 for more information about FPGA.

We are continuing the work done by Leduc et al [18] in developing properties that must be passed by a TDES project to be a good fit of a project ready to be implemented in hardware or software.

Chapter 2 in this thesis gives an introduction about the linguistic approach to system modelling. We also introduce TDES and its characteristics that enable us to produce SD controllers. TDES systems have the ability to be driven by a global central clock represented by the tick event that orchestrate the overall system to work in a synchronous manner.

Chapter 3 is about Sampled Data controllers; the concept and overview about how we are planning to implement them. Chapter 4 is about the model of finite state machines (FSM) introduced by Edward F. Moore in the 1950(s). Worth mentioning here that most of the hardware description languages such as VHDL, and VERILOG include the ability to model the hardware in building blocks, where each block is an FSM.

Chapter 5 is about introducing new algorithms to the verification process. We do this by proposing new propositions and proving them. We then implement them as algorithms to be used in our software program, DESpot [12]. In this chapter, we introduce our main addition to the area by introducing modular verification concepts. Modular verification is an important contribution to this work as it allows one to avoid checking properties using the synchronous product of the entire system, and instead to check these properties on individual components. If the individual components all pass, then the synchronous product of the system also passes.

Chapter 6 describes our effort in enhancing the algorithms from Wang [21] as well as our newly built ones.

Chapter 7 is about the algorithms built to translate our supervisors, and consequently the TDES project, into a hardware module (VERILOG). The reason we split this chapter from the previous one is that it has many algorithms that are all focused on producing FSM machines in XML format, and VERILOG files.

Chapter 8 presents a lock system that we modelled as TDES. We verified that it passes all the properties we developed so far to assure its validity as a hardware SD controller. We used this example to show the files we generated and explain the translation process.

Chapter 9 contains our conclusions, and future work discussion.

## Chapter 2

# Introduction to Discrete-Event Systems

Discrete-Event Systems are systems that are driven by events, and these systems include but not limited to manufacturing systems, traffic lights systems, database management systems, security systems and production line systems [25].

## 2.1 Linguistic and Algebraic Preliminaries

In this thesis we consider discrete-event systems (DES) from a linguistic approach. We look at the events in the system as symbols from an alphabet, is a sequence of events as words from a language.

### 2.1.1 Alphabets and Strings

An alphabet is a collection of symbols we refer as  $\Sigma$ . An example of an alphabet is  $\Sigma = \{\sigma, \beta, \gamma\}$ . A string is an arbitrary non-empty sequence constructed from an alphabet. Example strings constructed from the previous mentioned alphabet are as follows:  $\alpha\sigma\sigma, \gamma\beta\beta\sigma$  ...etc. We refer to the set of finite, non empty strings that can be constructed from this alphabet as  $\Sigma^+$ . The empty string  $\epsilon$  is not in this set :  $\epsilon \notin \Sigma$ . When we add the empty string to  $\Sigma^+$  we get the set  $\Sigma^*$ .

**Definition 2.1.1.** The *length* of a string is a unary function that takes  $s \in \Sigma^*$  and returns the number of symbols this string contains.

$$| : \Sigma^* \to \mathbb{N}$$

Let  $s = \sigma_1 \sigma_2 \dots \sigma_n$ ,  $\in \Sigma^+$  such that  $\sigma_i \in \Sigma$ , for  $i = \{1, 2, \dots, n\}$ . We thus have |s| = nThe empty string  $\epsilon$  is the string that does not have any symbols:  $|\epsilon| = 0$ .

**Definition 2.1.2.** The *concatenation* function is a binary function that takes two strings  $s_1, s_2$  from  $\Sigma^*$  and returns the string  $s_1s_2$ .

$$cat: \Sigma^* \times \Sigma^* \to \Sigma^*$$

Let  $s_1 = \sigma_1 \sigma_2 \dots \sigma_m$  with  $\sigma_i \in \Sigma$  and  $i = \{1, 2, \dots, m\}$  and  $s_2 = \beta_1 \beta_2 \dots \beta_n$  with  $\beta_j \in \Sigma$ and  $j = \{1, 2, \dots, n\}$ . Then  $cat(s_1, s_2) = s_1 s_2 = \sigma_1 \sigma_2 \dots \sigma_m \beta_1 \beta_2 \dots \beta_n$ , and  $|s_1 s_2| = m + n$

It follows from the above definitions that for any  $s \in \Sigma^*$   $s = \epsilon s = s\epsilon$ .

**Definition 2.1.3.** Let  $s, t \in \Sigma^*$ . We say s is a *prefix* of t, denoted as  $s \leq t$ , if  $(\exists u \in \Sigma^*) s u = t$

It is then obvious that any string is a prefix to itself,  $s \leq s$  since  $s\epsilon = s$ , and  $\epsilon \in \Sigma^*$ .

**Definition 2.1.4.** For alphabet  $\Sigma_1$  and alphabet  $\Sigma_2$ , we define the *set subtraction* operation as  $\Sigma_1 - \Sigma_2 := \{ \sigma | \sigma \in \Sigma_1 \land \sigma \notin \Sigma_2 \}.$

### 2.1.2 Languages

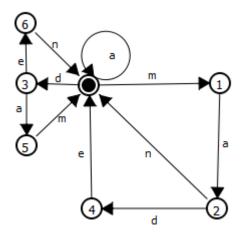

A language  $L \subseteq \Sigma^*$  is any subset of  $\Sigma^*$ . We can represent a language using the concept of an Automata. For example the ADAM language from Figure 2.1 will be represented by the following tuple automata  $ADAM = (Y, \Sigma, \eta, y_0, Y_m)$ . We have  $y_0$  is the initial state, Y is the set of all states in the automata, while  $Y_m \subseteq Y$  are the marked states. In this ADAM automata we have only one marked state that is also the initial state. The function  $\eta: Y \times \Sigma^* \to Y$  is the transition function and is a partial function.

We also partition  $\Sigma$  into controllable events,  $\Sigma_c$ , and uncontrollable events  $\Sigma_u$ . Controllable events are events that an external agent can disable and prevent from occurring. Uncontrollable events can not be disabled.

**Definition 2.1.5.** The *prefix closure* of a language, denoted as  $\overline{L}$ , is the set of all strings in  $\Sigma^*$  that can be continued to construct a string in L.

$$\overline{L} = \{ s \in \Sigma^* | (\exists t \in L) s \le t \}$$

Since it is clear from the previous section that any string is a prefix of itself, then the prefix closure contains the language itself. ie  $L \subseteq \overline{L}$ .

Figure 2.1: ADAM Language Automata

**Definition 2.1.6.** For a Language  $L \subseteq \Sigma^*$  we define the Nerode equivalence relation mod L as:

$$(\forall s, t \in \Sigma^*) s \equiv_L t \text{ or } s \equiv t \pmod{L} \iff [(\forall u \in \Sigma^*) s u \in L \iff t u \in L]$$

### **2.1.3** $\lambda$ – equivalence Relation

Let X be a nonempty set, and let  $E \subseteq X \times X$  be a binary relation on X.

**Definition 2.1.7.** The relation E is an *equivalence relation* on X if:

- $(\forall x \in X) x E x$  (*E* is reflexive)

- $(\forall x, x' \in X) x E x' \implies x' E x$  (*E* is symmetric)

- $(\forall x, x', x'' \in X) x E x' \& x' E x'' \implies x E x''$  (E is transitive).

For xEx' we may also write  $x \equiv x' \pmod{E}$ .

We now introduce the  $\lambda$  – equivalence relation.

**Definition 2.1.8.** Let  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  and let  $\lambda$  be an equivalence relation on Q such that for  $q, q' \in Q$ ,  $q \equiv q' \mod \lambda$  if and only if

1.

$$(\forall s \in \Sigma^*) \delta(q, s)! \iff \delta(q', s)!$$

2.  $(\forall s \in \Sigma^*)[\delta(q,s)! \& \delta(q,s) \in Q_m] \iff [\delta(q',s)! \& \delta(q',s) \in Q_m]$

Basically, for states q and q' such that  $q \equiv q' \mod \lambda$ , they have the same future with respect to the closed loop behavior, namely  $L(\mathbf{G})$ . They also have the same future with respect to the marked behaviour, namely  $L_m(\mathbf{G})$ .

### 2.2 Timed Discrete Event Systems

The common way is to introduce untimed DES, then introduce timed discrete-event system (TDES) as a special case of DES. But since this thesis is all about TDES and modelling the TDES in a way to be easy to turn it into an SD controller, we will start with TDES.

#### 2.2.1 TDES

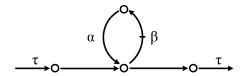

A TDES has a *tick* event in the set of events,  $\Sigma$ , and all the other events are considered activity events ( $\Sigma_{act}$ ). This makes  $\Sigma = \Sigma_{act} \dot{\cup} \{tick\}$ . We sometimes use  $\tau$  to

stand for the tick when brevity is needed. The occurrence of the *tick* event correspond to the tick of global clock.

We also have the concept of *forcible events*,  $\Sigma_{for} \subseteq \Sigma_{act}$ . These are events we can ensure occur before the next *tick*. In TDES forcible events can be controllable or uncontrollable. However, for sampled-data systems we require that all forcible events be also controllable. This simplifies our definitions while still providing a flexible modelling approach.

We model forcing by having an external agent disables the *tick* event when a forcible event is required to occur before the *tick*. The agent is not preventing the *tick* from occurring, but instead removing the path of behaviour where a tick occurs before the event to be be forced, so that the TDES behaviour matches what will actually physically occur. Of course there must be a forcible event possible to occur, and preempt the *tick* event. We capture this requirement in the TDES controllability definition in the Section 2.2.19.

We also introduce the concept of *prohibitable events*,  $\Sigma_{hib} \subseteq \Sigma_{act}$ . These are activity events that are controllable. We thus have  $\Sigma_c = \{\tau\} \cup \Sigma_{hib}$ . In the sampled-data setting, we thus have  $\Sigma_{hib} = \Sigma_{for}$ .

We usually model a TDES formally as a generator  $\mathbf{G}$ , which is a five tuple defined as the following:

$$\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$$

where

- Q is the finite *state set* of the TDES.

- $\Sigma$  is the finite set of distinct symbols representing event labels. This set is partitioned into two sets:

$$\Sigma = \Sigma_c \mathrel{\dot{\cup}} \Sigma_u$$