A Compositional Approach for Verifying Sampled-Data Supervisory Control

# A Compositional Approach for Verifying Sampled-Data Supervisory Control

by

## MAHVASH BALOCH, M.Sc.

A Thesis Submitted to the School of Graduate Studies in Partial Fulfilment of the Requirements for the degree of Master of Science

Department of Computing and Software McMaster University

© Copyright by Mahvash Baloch, March 2012

MASTER OF SCIENCE (2012)

(Computer Science)

McMaster University Hamilton, Ontario

| TITLE:                     | A Compositional Approach for Verifying Sampled-Data |  |  |  |  |  |  |  |  |

|----------------------------|-----------------------------------------------------|--|--|--|--|--|--|--|--|

|                            | Supervisory Control                                 |  |  |  |  |  |  |  |  |

| AUTHOR:                    | Mahvash Baloch, M.Sc. (Peshawar University)         |  |  |  |  |  |  |  |  |

| SUPERVISOR: Dr. Ryan Leduc |                                                     |  |  |  |  |  |  |  |  |

| NUMBER OF PAGES: i, 138    |                                                     |  |  |  |  |  |  |  |  |

# A Compositional Approach for Verifying Sampled-Data Supervisory Control

### Abstract

Sampled-data supervisory control deals with timed discrete event systems (TDES) where the supervisors are to be implemented as sampled-data controllers. A sampled-data controller views the system as a series of inputs and outputs and is controlled by a periodic clock. It samples its inputs, changes state, and updates its outputs on each clock edge (the tick event). The sampled-data supervisory control framework provides a set of conditions that the TDES system must satisfy to ensure its correct behaviour in order to be implemented as sampled data controllers. A serious limitation for automatic verification of systems is the size of the system's synchronous product. To overcome this limitation, we propose the use of a compositional approach to the verification of sampled-data supervisory control. In this approach, first we recast the required conditions for sampled-data supervisory control in terms of other properties such as language inclusion, nonblocking or controllability, which already have existing compositional methods and algorithms. This makes the sampled-data properties suitable for compositional verification, considerably increasing the size of systems that can be handled using sampled-data supervisory control. We also develop and implement a set of algorithms for the compositional verification of these sampled-data properties. We provide an example of the SD Controlled Flexible Manufacturing System to test our algorithms.

#### Acknowledgments

First I would like to thank my supervisor, Dr. Ryan Leduc, for his insight and guidance. I am very grateful to him for his continuous support and sound advice throughout my masters study and research. Without his encouragement I would have never been able to complete this thesis.

I would also like to thank my unofficial co-supervisor, Dr. Robi Malik, for his help and contribution throughout my research and especially in the development of the software as a part of his DES research project, WATERS. I am deeply indebted to him for his time and patience throughout the course of my research. Without his detailed and timely replies to my queries I would not have been able to complete my research. It was a pleasure to work with him.

I am very grateful for the love and support of my parents and my siblings who encouraged me at every step. Thank you for everything.

My deep gratitude goes to my husband, Shahid, for his constant encouragement, support and love. A big thank you to him for his understanding and confidence in me. Finally I would like to thank my sons, Aareel and Romaan, for being a great source of motivation to me. I dedicate this thesis to them.

# TABLE OF CONTENTS

| 1        | Intr | $\operatorname{pduction}$             |

|----------|------|---------------------------------------|

|          | 1.1  | Related Work                          |

|          | 1.2  | Structure of the Thesis               |

| <b>2</b> | Pre  | iminaries                             |

|          | 2.1  | Languages                             |

|          | 2.2  | Discrete Event Systems                |

|          |      | 2.2.1 Generator                       |

|          |      | 2.2.2 Synchronous Product             |

|          |      | 2.2.3 Controllability and Supervision |

|          |      | 2.2.4 Language Inclusion              |

|          | 2.3  | Timed Discrete Event Systems          |

|          |      | 2.3.1 Controllability and Supervision |

| 3        | San  | pled-Data Supervisory Control         |

|          | 3.1  | SD Controller                         |

|          | 3.2  | System Assumptions                    |

|          | 3.3  | SD Preliminaries                      |

|          | 3.4  | SD Properties                         |

|          |      | 3.4.1 Plant Completeness              |

|          |      | 3.4.2 Activity Loop Free              |

|          |      | 3.4.3 Proper Time Behaviour           |

|          |     | 3.4.4 S-singular Prohibitable Behaviour                                                          | 22 |

|----------|-----|--------------------------------------------------------------------------------------------------|----|

|          |     | 3.4.5 SD Controllable Languages                                                                  | 23 |

|          |     | 3.4.5.1 SD Controllability Examples                                                              | 25 |

| 4        | Cor | npositional Verification for SD Properties                                                       | 27 |

|          | 4.1 | Plant Completeness                                                                               | 27 |

|          | 4.2 | Activity Loop Free                                                                               | 28 |

|          | 4.3 | S-singular Prohibitable Behaviour                                                                | 29 |

|          | 4.4 | Proper Time Behaviour                                                                            | 38 |

| <b>5</b> | Cor | npositional Verification of SD Controllability                                                   | 12 |

|          | 5.1 | SD Controllability Point (ii)                                                                    | 42 |

|          |     | 5.1.1 SD Controllability Point (ii.a)                                                            | 44 |

|          |     | 5.1.2 SD Controllability Point (ii.b)                                                            | 54 |

|          | 5.2 | SD Controllability Point (iii)                                                                   | 64 |

|          |     | 5.2.1 SD Controllability Point (iii.1) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 64 |

|          |     | 5.2.1.1 SD Controllability Point (iii.1a) $\ldots \ldots \ldots \ldots$                          | 65 |

|          |     | 5.2.1.2 SD Controllability Point (iii.1b) $\ldots$                                               | 77 |

|          |     | 5.2.2 SD Controllability Point (iii.2)                                                           | 86 |

|          | 5.3 | SD Controllability Point (iv)                                                                    | 89 |

| 6        | Alg | $\operatorname{orithms}$                                                                         | 96 |

|          | 6.1 | Plant Completeness                                                                               | 97 |

|          | 6.2 | ALF 9                                                                                            | 97 |

|          | 6.3 | S-singular Prohibitable Behaviour                                                                | 98 |

|   | 6.4               | Prope | r Time Behaviour                                                                                                                              | 8  |

|---|-------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 6.5               | SD Co | ontrollability Point (ii) 99                                                                                                                  | 9  |

|   |                   | 6.5.1 | SD Controllability Point (ii.a)                                                                                                               | 0  |

|   |                   | 6.5.2 | SD Controllability Point (ii.b)                                                                                                               | 0  |

|   | 6.6               | SD Co | ontrollability Point (iii.1) $\ldots \ldots 10$                                | 1  |

|   |                   | 6.6.1 | SD Controllability Point (iii.1a) Algorithm 10                                                                                                | 1  |

|   |                   | 6.6.2 | SD Controllability Point (iii.1b) Algorithm 102                                                                                               | 2  |

|   | 6.7               | SD Co | ontrollability Point (iii.2)                                                                                                                  | 3  |

|   |                   | 6.7.1 | Monolithic Verification Algorithm                                                                                                             | 4  |

|   |                   |       | 6.7.1.1 AnalyzeSampledState Algorithm 10                                                                                                      | 6  |

|   |                   |       | 6.7.1.2 CheckNerodeCells Algorithm                                                                                                            | 7  |

|   |                   |       | 6.7.1.3 ReCheckNerodeCells Algorithm                                                                                                          | 18 |

|   |                   |       | 6.7.1.4 RecheckNerodeCell Algorithm                                                                                                           | 9  |

|   |                   | 6.7.2 | Incremental Verification Algorithm                                                                                                            | 1  |

|   | 6.8               | SD Co | ontrollability Point (iv)                                                                                                                     | 3  |

| 7 | SD                | Contr | olled FMS Example                                                                                                                             | 5  |

| ' | 5 <b>D</b><br>7.1 |       | -                                                                                                                                             |    |

|   |                   |       | · · · · · · · · · · · · · · · · · · ·                                                                                                         |    |

|   | 7.2               | 1     | visors $\ldots \ldots \ldots$ |    |

|   |                   | 7.2.1 | B2                                                                                                                                            |    |

|   |                   | 7.2.2 | B6 and B7                                                                                                                                     |    |

|   |                   | 7.2.3 | B8                                                                                                                                            | 9  |

|   |                   | 7.2.4 | TakeB2                                                                                                                                        | 0  |

|   |                   | 7.2.5 | B4                                                                                                                                            | 2  |

|   |     | 7.2.6   | B4Path     |          | <br>    | <br>    |   |     |     | • |     | • | • • | • | ••• | • | 123 |

|---|-----|---------|------------|----------|---------|---------|---|-----|-----|---|-----|---|-----|---|-----|---|-----|

|   |     | 7.2.7   | LathePicl  | κ        | <br>    | <br>    |   |     |     |   |     | • |     | • |     | • | 123 |

|   |     | 7.2.8   | TakeB4P    | utB6     | <br>    | <br>    |   |     |     |   |     |   |     | • |     | • | 123 |

|   |     | 7.2.9   | TakeB4P    | utB7     | <br>    | <br>    |   |     |     |   |     |   |     | • |     | • | 124 |

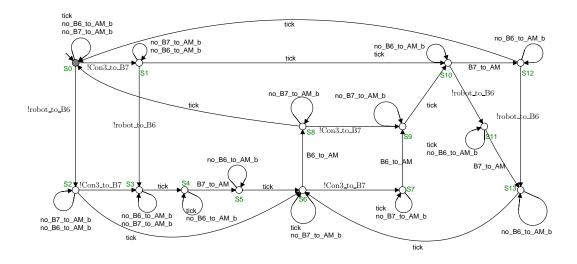

|   |     | 7.2.10  | ForceB6t   | оАМ      | <br>    | <br>    |   |     |     |   |     |   |     | • |     | • | 125 |

|   |     | 7.2.11  | ForceB7te  | оАМ      | <br>    | <br>    |   |     |     |   |     |   |     | • |     | • | 125 |

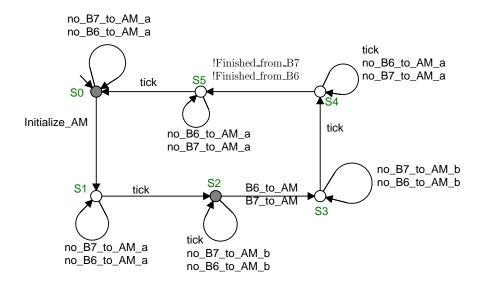

|   |     | 7.2.12  | ForceIniti | ializeAM | <br>    | <br>    |   |     |     |   |     | • |     | • |     | • | 125 |

|   |     | 7.2.13  | AMChoo     | ser      | <br>    | <br>    |   |     |     |   |     |   |     | • |     | • | 127 |

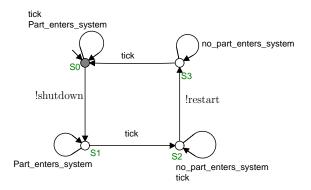

|   |     | 7.2.14  | handleSys  | stDown   | <br>    | <br>    |   |     |     |   |     |   |     | • |     | • | 127 |

|   | 7.3 | Result  | s          |          | <br>    | <br>    |   |     |     | • |     | • |     | • |     | • | 128 |

| 8 | Com | -1      | ns         |          |         |         |   |     |     |   |     |   |     |   |     |   | 101 |

| 0 | Con | clusion | 15         |          | <br>• • | <br>• • | • | ••• | • • | · | • • | • | ••• | • | ••  | • | 191 |

|   | 8.1 | Conclu  | sions      |          | <br>    | <br>    |   |     |     | • |     | • |     | • |     | • | 131 |

|   | 8.2 | Future  | Work       |          | <br>    | <br>    |   |     |     |   |     |   |     |   |     |   | 132 |

# LIST OF FIGURES

| 2.1 | An Example DES                            | 8   |

|-----|-------------------------------------------|-----|

| 3.1 | Sampling Events                           | 16  |

| 3.2 | Plant                                     | 20  |

| 3.3 | Supervisor                                | 20  |

| 3.4 | Example TDES for SD Properties            | 22  |

| 3.5 | SD Controllability Example 1 - Plant      | 24  |

| 3.6 | SD Controllability Example 1 - Supervisor | 24  |

| 3.7 | SD Controllability Example 2 - Plant      | 25  |

| 3.8 | SD Controllability Example 2 - Supervisor | 25  |

| 4.1 | TDES $T^{\sigma}$                         | 29  |

| 4.2 | TDES $T_{\Upsilon}$                       | 39  |

| 5.1 | TDES $T_{\Sigma}^E$                       | 50  |

| 5.2 | TDES $T_{\alpha,G}$                       | 70  |

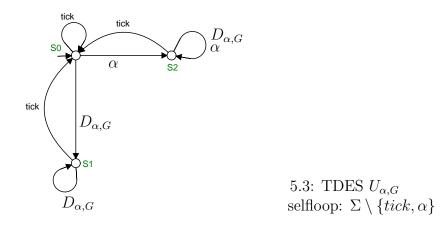

| 5.3 | TDES $U_{\alpha,G}$                       | 78  |

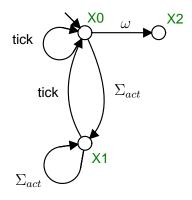

| 5.4 | TDES T                                    | 90  |

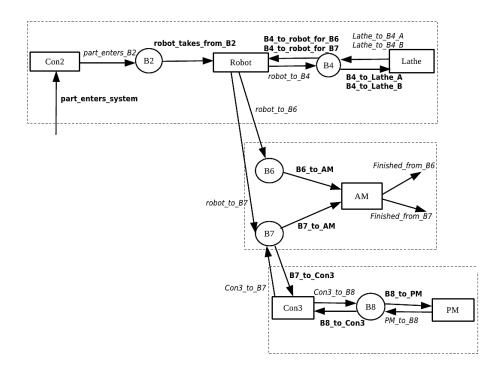

| 7.1 | Flexible Manufacturing System Overview    | 115 |

| 7.2 | Robot                                     | 116 |

| 7.3 | Painting Machine - PM                     | 116 |

| 7.4 | Lathe                                     | 117 |

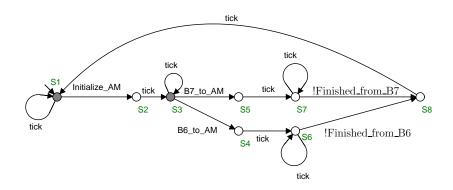

| 7.5 | Finishing Machine - AM                    | 117 |

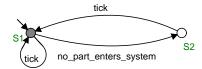

| 7.6  | AddNoPartEntersSystem        |

|------|------------------------------|

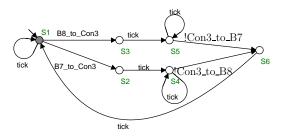

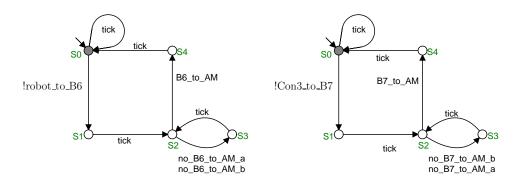

| 7.7  | Conveyer- Con3               |

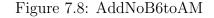

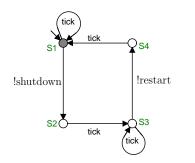

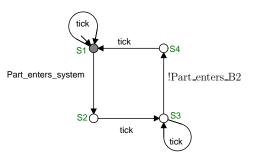

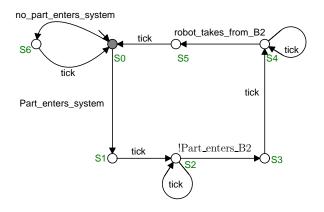

| 7.8  | AddNoB6toAM                  |

| 7.9  | AddNoB7toAM                  |

| 7.10 | SystDownNup                  |

| 7.11 | Conveyer - Con2              |

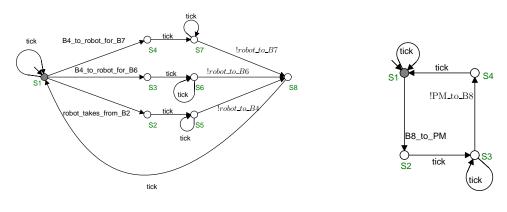

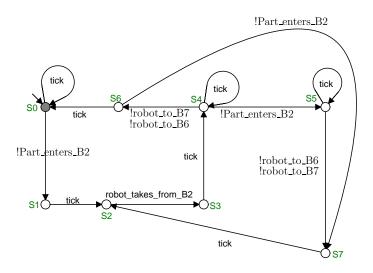

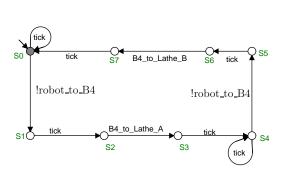

| 7.12 | Supervisor B2                |

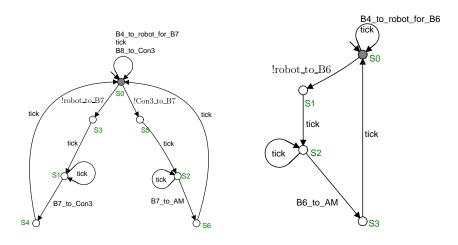

| 7.13 | Supervsior B7                |

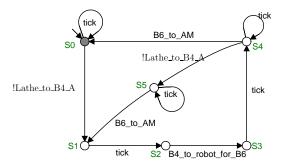

| 7.14 | Supervisor B6                |

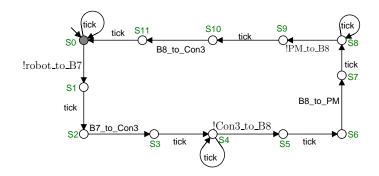

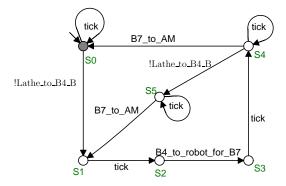

| 7.15 | Supervisor B8                |

| 7.16 | Supervsior TakeB2            |

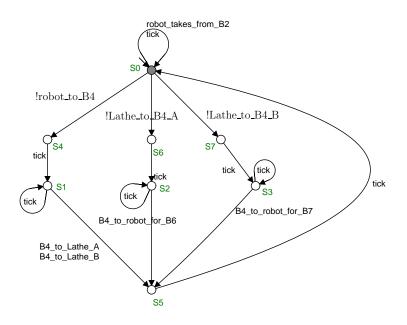

| 7.17 | Supervsior B4                |

| 7.18 | Supervisor B4Path            |

| 7.19 | Supervsior LathePick         |

| 7.20 | Supervisor TakeB4PutB6       |

| 7.21 | Supervisor TakeB4PutB7       |

| 7.22 | Supervisor ForceB6toAM       |

| 7.23 | Supervsior ForceB7toAM       |

| 7.24 | Supervisor ForceInitializeAM |

| 7.25 | Supervisor AMChooser         |

| 7.26 | Supervisor handleSystDown    |

## LIST OF TABLES

| 7.1 | Statistics from | FMS | Example |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 128 | 3 |

|-----|-----------------|-----|---------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|---|

|-----|-----------------|-----|---------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|-----|---|

## CHAPTER 1

## Introduction

A discrete event system (DES) [CL10, Won11] is a dynamic system whose state space is discrete and whose state can only change in response to instantaneous occurence of events over time. The applications of DES can be found in many areas including manufacturing systems, traffic systems, communication protocols, data communication networks and database management systems.

A DES model can be represented as either timed DES (TDES) model [Ost89, Ost90, OW90] or untimed DES model. In an untimed DES model, we are only concerned with the sequence of events taking place in order to satisfy a given set of specifications. Such a model is only concerned in the logical behavior of the system such as finding if a particular state (or set of states) of the system can be reached or not. In such models, the actual timing of events is not considered. In a TDES model, timing information is important as well as the sequence of events . Its important to consider the time at which the system reaches a particular state and the amount of time it spends there. Its also important to be able to specify when an event will occur, and not just the ordering of the event occurences.

The supervisory control theory introduced by Ramadge and Wonham [RW89, Won11, WR87] provides a formal frame work for analyzing discrete event systems. In this theory an automaton is used to model the system(the plant) to be controlled and the specification of the desired system behaviour. The aim is to impose a given specification on the system by means of a supervisor which restricts the behaviour of a system. The theory provides methods and algorithms

to obtain a supervisor that ensures that the system always produces the desired behaviour. It is desirable for a system to satisfy two properties, controllability (undesired actions don't occur) and nonblocking (system doesn't deadlock or livelock).

The supervisory control is often used for complex, safety critical systems, therefore it is very important to verify automatically that the supervisor satisfies the required properties. However, large and complex systems have a very large state space as they are usually modeled as the synchronous product of a group of component DES, thus the state space size increases exponentially in the number of the components. Such a problem is known as the state space explosion problem. This makes the verification of complex systems more challenging. To address the state space explosion problem, different approaches to system verification have been proposed and investigated.

Symbolic verification [McM93] is one method of verifying complex finite state safety critical systems. It is possible to verify extremely large systems having as many as 10<sup>20</sup> states by using Binary decision diagrams (BDD) [Bry92]. Several systems of industrial complexity have been verified[CCMM95, HGCC96, HGKCL95] using this technique. In spite of being quite successful, symbolic model checking has its limitations. In some cases it can easily encounter the state space explosion problem.

Another technique which has been successful to overcome state space explosion is compositional verification [CLM89, GL94, KM00]. The compositional verification method splits up the verification of a system into the verification of its components. That means we can verify that a system satisfies the properties of interest by checking its components one by one, rather than checking the whole system. Separate verification of components limits state explosion.

Once we have designed our system, we next need to physically implement our

supervisors, which brings us to the focus of this thesis. The sampled-data (SD) supervisory control framework was proposed in [Wan09, LW10] to implement TDES supervisors as sampled-data controllers. An SD controller is controlled by a periodic clock and views the system as a series of inputs and outputs. The sampled-data supervisory control provides a set of conditions that can be used to ensure correct behaviour (i.e. our controller retains nonblocking and controllability) when implementing TDES supervisors as SD controllers. The algorithms in [Wan09] for verification of these properties have been implemented using symbolic methods.

In this thesis, we propose a compositional approach for verifying the properties of sampled-data supervisory control in order to increase the size of systems to which this theory can be applied. Our approach to develop a compositional verification method for sample-data supervisory control is to first redefine the required property for the given system in terms of either controllability, nonblocking or a language inclusion problem, and then show that this new representation is equivalent. We can then use the existing compositional approaches for verifying controllability, nonblocking, and language inclusion to check these conditions.

#### 1.1 Related Work

The implementation of a controller in supervisory control has always been a challenging problem. A lot of research [BHG<sup>+</sup>93, Bal94, GR87] has been done to establish the fact that in order to implement a controller, its behaviour needs to satisfy additional properties not included in the traditional supervisory control theory. In [Mal03] the author suggests conditions to be satisfied for implementing nonblocking controllers for untimed nonblocking supervisors.

Sampled-data supervisory control theory [LW10, Wan09] establishes a set of conditions that need to be satisfied in order to implement TDES supervisors as SD controllers. This theory is developed using the theory of supervisory control of timed DES [BW94, Bra92] as a basis.

Verification and synthesis of discrete event systems has been an interesting area for researchers in the recent years. [ÅFF02] takes advantage of the modular structure of the system to develop an efficient algorithm for verifying controllability. In [BMM04], the authors present a new approach for the verification of safety properties, controllability and language inclusion, based on subsystem verification. They combine the use of counter-examples and heuristics to identify subsystems incrementally.

The verification of nonblocking has been a more challenging problem. A lot of effort has gone into the study of compositional semantics of nonblocking [KS94, RMR06] and its verification [FM09, PCL06]. In [FM09], the authors propose a compositional approach to verify nonblocking for a large discrete event system. The method avoids computing the synchronous product directly, but instead the synchronous product is computed gradually, and the results are simplified using conflict-preserving abstractions based on process-algebraic results about fair testing. The authors propose using the the same method to verify controllability.

In [ML08] authors Malik and Leduc discuss the conversion of nonblocking property into a more expressive property called generalised nonblocking and present its compositional verification method in [ML09]. Its implementation is presented in [Fra11]. In a similar manner, Malik and Leduc provide a compositional approach for verifying HISC [Led02, LBLW05, LDS09, LLD06, LLW05, Led09] which is presented in [LM10].

An efficient algorithm which uses the compositional technique for the detection of control loops is given in [MM06]. The technique takes advantage of the modular structure of discrete event system models to identify and check subsystems, in such a way that the results of checking the subsystems can be used to draw conclusions about the properties of the entire system.

The use of language projection can greatly improve the performance of compostional verification to verify properties of a large discrete event system. In [WM08], the authors propose the use of abstraction by language projection to prove or disprove that a large system of composed finite-state machines satisfies a given safety property.

### **1.2** Structure of the Thesis

In this thesis we present a compositional approach for verifying sampled-data supervisory control systems. In Chapter 2, we present the definitions and notations that are used throughout the thesis. Chapter 3 is an introduction to sampleddata systems and the required conditions for sampled-data supervisory control. It also gives examples for the properties to illustrate their meaning.

In Chapters 4 and 5, we provide the new definitions for the SD properties. We express each property in terms of a language inclusion, nonblocking or controllability property and provide detailed proofs to show that the new definitions are equivalent to the ones originally given in [Wan09, LW10].

In Chapter 6, we present our algorithms to verify the SD properties and discuss the implementation of the algorithms. In Chapter 7, we present the SD controlled FMS example from [Wan09] and discuss the results of applying our software to it. Finally we conclude with conclusions and future work in Chapter 8.

## CHAPTER 2

## Preliminaries

A discrete event system is a dynamic system whose state space is discrete and whose state can only change in response to instantaneous occurence of events over time. DES are modelled as automata that generate a formal language of distinct symbols. Supervisory control theory [RW89, Won11, WR87] provides a theoretical framework for the control of discrete event systems. This chapter presents an overview of the the terminology and concepts used in this thesis.

#### 2.1 Languages

Let alphabet  $\Sigma$  be a non-empty finite set of distinct symbols. A *string* is a finite sequence of symbols which belong to  $\Sigma$ . The set  $\Sigma^*$  defines the set of all finite sequence of events of the form  $\sigma_1 \sigma_2 ... \sigma_n$   $(n \ge 1)$  as well as the *empty string*,  $\epsilon$ . Given a string s, |s| = n defines the *length* of the string. The empty string  $\epsilon$  has length 0. Let  $\Sigma^+$  denote the set of all finite non-empty symbol sequences. We can then define  $\Sigma^* := \Sigma^+ \cup {\epsilon}$ . The *catenation* operation of strings is defined as

cat :  $\Sigma^* \times \Sigma^* \to \Sigma^*$

where  $cat(\epsilon, s) = cat(s, \epsilon) = s$ , and cat(s,t) = st.

Let s,  $t \in \Sigma^*$ . String t is said to be a *prefix* of s, denoted as  $t \leq s$ , if  $(\exists u \in \Sigma^*)su = t$ . Clearly  $\epsilon$  is a prefix of all strings, as  $(\forall s \in \Sigma^*)\epsilon \leq s$ . Also, every string  $s \in \Sigma^*$  is a prefix of itself, as  $s \leq s$ .

A language over  $\Sigma$  is any subset  $L \subseteq \Sigma^*$ . The *prefix closure* of L, written as

$\overline{L}$ , is defined as  $\overline{L} = \{s \in \Sigma^* | (\exists t \in L) s \leq t\}$ . Clearly, a language is a subset of its prefix closure, i.e.  $L \subseteq \overline{L}$ . A language is called *prefix closed* if  $L = \overline{L}$ .

The usual set operations, such as union, intersection, difference etc., are applicable to languages since languages are sets. For sets  $\Sigma$  and  $\Sigma_1$ , the notation  $\Sigma - \Sigma_1$ , or  $\Sigma \setminus \Sigma_1$  refers to the set  $\{x | x \in \Sigma \land x \notin \Sigma_1\}$ , the set of elements of  $\Sigma$  that are not in  $\Sigma_1$ . Similarly  $Pwr(\Sigma)$  refers to the set of all subsets of  $\Sigma$ , including  $\emptyset$ , the empty set.

Let  $L \subseteq \Sigma^*$ . The *eligibility operator*,  $\operatorname{Elig}_L : \Sigma^* \to \operatorname{Pwr}(\Sigma)$ , is defined for s  $\in \Sigma^*$  as  $\operatorname{Elig}_L(s) := \{ \sigma \in \Sigma \mid s\sigma \in L \}.$

We define the Nerode equivalence relation on  $\Sigma^*$  with respect to L (or mod L) as follows. For strings s, t  $\in \Sigma^*$ ,

$s \equiv_L t \text{ or } s \equiv t \pmod{L}$  iff  $(\forall u \in \Sigma^*) su \in L$  iff  $tu \in L$ .

The above definition states that we say s and t are Nerode equivalent with respect to the language L if and only if they can be extended by any string  $u \in \Sigma^*$  such that either both strings are in L or neither string is in L. In other words, if strings s and t are equivalent *mod* L then both s and t can be continued in exactly the same way by right concatenation with respect to membership in L.

#### 2.2 Discrete Event Systems

#### 2.2.1 Generator

Formally, we model DES as a generator  $\mathbf{G}$ , which is a tuple

$$\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$$

where Q is the state set,  $\Sigma$  is the event set,  $\delta : Q \times \Sigma \to Q$  is the (partial) transition function,  $q_0$  is the initial state, and  $Q_m \subseteq Q$  is the set of marked states.

As  $\delta: Q \times \Sigma \to Q$  is a partial function,  $\delta(q, \sigma)!$  means  $\delta(q, \sigma)$  is defined for

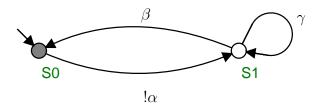

Figure 2.1: An Example DES

$\sigma \in \Sigma$  at state  $q \in Q$ . We can extend the transition function to  $\delta : Q \times \Sigma^* \to Q$ as

$$\begin{split} &\delta(q,\epsilon)=q \text{ for } \mathbf{q}\in\mathbf{Q}.\\ &\delta(q,s\sigma)=\delta(\delta(q,s),\sigma) \text{ for } s\in\Sigma^* \text{ , } \sigma\in\Sigma, \text{ and } \mathbf{q}\in\mathbf{Q}. \end{split}$$

provided  $q' := \delta(q, s)!$  and  $\delta(q', \sigma)!$ .

A DES **G** can be represented by a transition graph. The states in **Q** are represented by the nodes(circles) in the graph. Transitions are represented by the edges. The small arrow pointing to a state labels the initial state. and the marked states are represented by a shaded circle. Usually, a controllable event is graphically shown by a slash on the transition edge. For the figures in this thesis, we have prefixed uncontrollable events with a "!" to distinguish between controllable and uncontrollable events.

For convenience, we use the notation  $\Sigma_G$  to define the event set that DES G is defined over. Similarly we will use the notations  $Q_G$ ,  $\delta_G$ ,  $q_{0,G}$  and  $Q_{m,G}$  for the other components of DES **G**.

The closed behaviour of DES G is described by the language

$$\mathcal{L}(\mathcal{G}) = \{ s \in \Sigma^* \mid \delta(q_0, s)! \}$$

The marked behaviour of DES G is defined as

$$L_m(G) = \{ s \in \Sigma^* \mid \delta(q_0, s)! \land \delta(q_0, s) \in Q_m \}$$

Note that  $L_m(G) \subseteq L(G)$  and  $\epsilon \in L(G)$  as long as  $Q \neq \emptyset$ .

A state  $\mathbf{q} \in \mathbf{Q}$  is reachable if there is a string  $\mathbf{s} \in \Sigma^*$  with  $\delta(q_0, s)!$  and

$\delta(q_0,s)=q.~\mathbf{G}$  itself is reachable if q is reachable for all q  $\in$  Q .

A state  $q \in Q$  is coreachable if there is  $s \in \Sigma^*$  such that  $\delta(q, s) \in Q_m$ . **G** is coreachable if q is coreachable for every  $q \in Q$ .

We define equivalence relation  $\lambda$  on Q as:

$$(\forall q, q' \in Q)q \equiv q' \pmod{\lambda}$$

iff

- i)  $(\forall s \in \Sigma^*) \eta(q, s)! \Leftrightarrow \eta(q', s)!$

- ii)  $(\forall s \in \Sigma^*) \eta(q, s)! \land \eta(q, s) \in Q_m \Leftrightarrow \eta(q's)! \land \eta(q', s) \in Q_m$

Nonblocking [Won11] is a very crucial property for discrete event systems. It is the ability to reach a marked state from all reachable states. Formally defined, **G** is said to be nonblocking if every reachable state is coreachable. The language form of the definition is:

$$\overline{L_m(G)} = \mathcal{L}(\mathcal{G})$$

We say that a set of DES is nonconflicting, if the synchronous product (see definition in next section) is nonblocking.

#### 2.2.2 Synchronous Product

In real life, it is more convenient to model a system using more than one DES that interact with each other when they run concurrently. To model a system, we need a way to represent the entire system running in parallel. The synchronous product [Won11] is used to combine two or more DES into a single one. Each DES in the system usually shares some events in their alphabet with other DES in the system. These shared events must be executed by all components at the same time.

To define the synchronous product, we first need to define the natural projection operator and its inverse. Let  $\Sigma_i^* \subseteq \Sigma$ , i=1,2. We define the *natural projection*  $P_i: \Sigma^* \to \Sigma_i^*$  and  $\Sigma = \Sigma_1 \cup \Sigma_2$  as:

$$P_i(\epsilon) = \epsilon$$

$$P_{i}(\sigma) = \begin{cases} \epsilon & \text{if } \sigma \notin \Sigma_{i} \\ \sigma & \text{if } \sigma \in \Sigma_{i} \end{cases}$$

$$P_{i}(s\sigma) = P_{i}(s)P_{i}(\sigma) \qquad s \in \Sigma^{*}, \, \sigma \in \Sigma$$

$P_i(s)$  removes all events that belong to  $\Sigma - \Sigma_i$ , for string  $s \in \Sigma^*$ . The *inverse image* of  $P_i$  is  $P_i^{-1}$ :  $Pwr(\Sigma_i^*) \to Pwr(\Sigma^*)$ . For  $L \subseteq \Sigma_i^*$ , we get

$$P_i^{-1}(L) := \{ s \in \Sigma^* | P_i(s) \in L \}.$$

Let  $L_i \subseteq \Sigma_i^*$ . The synchronous product of  $L_1$  and  $L_2$  is defined as

$$L_1 \parallel L_2 = P_1^{-1}L_1 \cap P_2^{-1}L_2$$

For DES  $G_1 = (Q_1, \Sigma, \delta_1, q_{0,1}, Q_{m,1})$  and DES  $G_2 = (Q_2, \Sigma, \delta_2, q_{0,2}, Q_{m,2})$  de-

fined over the same event set  $\Sigma$ , the *product* of two DES is defined as

$G_1 \times G_2 = (Q_1 \times Q_2, \Sigma, \delta_1 \times \delta_2, (q_{0,1}, q_{0,2}), Q_{m,1} \times Q_{m,2})$

where  $\delta_1 \times \delta_2 : Q_1 \times Q_2 \times \Sigma \to Q_1 \times Q_2$  is defined as

$$(\delta_1 \times \delta_2)((q_1, q_2), \sigma) := (\delta_1(q_1, \sigma), \delta_2(q_2, \sigma))$$

whenever  $\delta_1(q_1, \sigma)!$  and  $\delta_2(q_2, \sigma)!$ , otherwise undefined.

By this definition, we have

$$L(G_1 \times G_2) = L(G_1) \cap L(G_2)$$

and  $L_m(G_1 \times G_2) = L_m(G_1) \cap L_m(G_2)$

For DES  $G_1 = (Q_1, \Sigma_1, \delta_1, q_{0,1}, Q_{m,1})$  and DES  $G_2 = (Q_2, \Sigma_2, \delta_2, q_{0,2}, Q_{m,2})$ the synchronous product  $G = G_1 \parallel G_2$  of the two DES is defined as :

$$\mathbf{G} := (Q_1 \times Q_2, \Sigma_1 \cup \Sigma_2, \delta, (q_{0,1}, q_{0,2}), Q_{m,1} \times Q_{m,2}),$$

where  $\delta((q_1, q_2), \sigma)$  is only defined and equals

$$(q'_1, q'_2)$$

if  $\sigma \in (\Sigma_1 \cap \Sigma_2), \delta_1(q_1, \sigma) = q'_1, \delta_2(q_2, \sigma) = q'_2$  or

$$(q'_1, q_2)$$

if  $\sigma \in \Sigma_1 - \Sigma_2, \delta_1(q_1, \sigma) = q'_1$  or

$$(q_1, q'_2)$$

if  $\sigma \in \Sigma_2 - \Sigma_1, \delta_2(q_2, \sigma) = q'_2$

When we synchronize two DES, we get a new DES with the synchronized langauges as its language i.e.

$$L(G) = L(G_1) \parallel L(G_2), \ L_m(G) = L_m(G_1) \parallel L_m(G_2)$$

Let  $G_1$  be a DES with event set  $\Sigma_1$  and  $\Sigma_2$  be another event set such that  $\Sigma_1 \cap \Sigma_2 = \emptyset$ . We define the selfloop operation on  $G_1$  as selfloop $(G_1, \Sigma_2) = (Q_1, \Sigma_1 \cup \Sigma_2, \delta_2, q_{0,1}, Q_{m,1}),$

where  $\delta_2: Q_1 \times (\Sigma_1 \cup \Sigma_2) \to Q_1$  is a partial function defined as:

$$\delta_2(q,\sigma) := \begin{cases} \delta_1(q,\sigma) & \sigma \in \Sigma_1, \delta_1(q,\sigma)! \\ q & \sigma \in \Sigma_2 \\ undefined & \text{otherwise} \end{cases}$$

In this thesis, when using the synchronous product to combine individual DES  $G_i$  (i=1,2) we will typically assume that first the DES is extended to be over the alphabet  $\Sigma$  by adding selfloops, and then combined using the product operator. Therefore  $G_1 \parallel G_2 = \text{selfloop}(G_1, \Sigma - \Sigma_1) \times \text{selfloop}(G_2, \Sigma - \Sigma_2).$

#### 2.2.3 Controllability and Supervision

The notion of supervisory control [Won11] is introduced by assuming that some events can be disabled i.e. not allowed to occur by an external agent (also known as a supervisor). The alphabet  $\Sigma$  is partitioned into two disjoint subsets  $\Sigma_c$  and  $\Sigma_u$ , where  $\Sigma_c$  is the set of controllable events (which can be enabled or disabled) and  $\Sigma_u$  is the set of uncontrollable events (which cannot be disabled). Once we reach a state in the DES where an uncontrollable event can occur, the event cannot be prevented.

Let the DES  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  represent the possible system behaviour (i.e. our plant) and let  $\mathbf{K} \subseteq \Sigma^*$  be a language describing the desired safe behaviour of our system. We say K is *controllable* with respect to **G** if

$$\overline{K}\Sigma_u \cap L(G) \subseteq \overline{K}.$$

The above definition says that K is controllable with respect to L(G) if every string in  $\overline{K} \cap L(G)$  followed by an uncontrollable event  $\sigma$  that is possible in L(G), then  $\sigma$  must be accepted in  $\overline{K}$  as well. We can also express this definition as  $(\forall s \in \overline{K} \cap L(G))Elig_{L(G)}(s) \cap \Sigma_u \subseteq Elig_{\overline{K}}(s)$

Note that the languages  $\emptyset$ , L, and  $\Sigma^*$  are all controllable with respect to G.

To represent our desired system behaviour, we define a DES  $\mathbf{S} = (X, \Sigma_S, \xi, x_0, X_m)$  called a supervisor. Supervisors monitor the events generated by the plant, and disable events according to some control law. We say supervisor  $\mathbf{S}$  is controllable for plant  $\mathbf{G}$  if

$$L(S) \Sigma_u \cap L(G) \subseteq L(S)$$

#### 2.2.4 Language Inclusion

Language inclusion is used to check if the language of a system is included by the language of a given DES. Let DES  $\mathbf{G}$  represent our system and DES  $\mathbf{R}$  define the requirements. Language inclusion is defined as follows:

**Definition 2.1.** Let **G** and **R** be two DES using the same alphabet  $\Sigma$ . We say **G** satisfies **R** if  $L(G) \subseteq L(R)$ .

In other words **G** satisfies **R**, if and only if every string in L(G) is also in L(R). Language inclusion is also used to check for language equality. For two languages  $L_1$  and  $L_2$ ,  $L_1 = L_2$  can be expressed as  $L_1 \subseteq L_2$  and  $L_2 \subseteq L_1$ .

### 2.3 Timed Discrete Event Systems

The timed DES (TDES) theory introduced by Brandin et al [BW94, Bra92], adds onto untimed DES theory. A special event *tick* is added to the event set which models the passage of time representing the tick of a global clock. The event set  $\Sigma$ , for a TDES, is expressed as the disjoint union of non-tick events called activity events ( $\Sigma_{act}$ ) and the *tick* event, i.e.  $\Sigma = \Sigma_{act} \cup \{tick\}$ . Additional control method is introduced by means of forcible events  $(\Sigma_{for})$ . A forcible event is defined as an event which is guaranteed to occur before the next *tick* thus preempting the *tick*. It models the situation in which something is forced to occur within a certain time frame. Hence it is possible not only to prevent some events (prohibitable events  $\Sigma_{hib} \subseteq \Sigma_{act}$ ) from occurring by disabling them, but also to force some events to occur before the next clock tick.

We formally define a TDES as the tuple  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  where, Q is the state set,  $\Sigma = \Sigma_{act} \cup \{tick\}$  is the event set,  $\delta : Q \times \Sigma \to Q$  is the (partial) transition function,  $q_0 \in Q$  is the initial state and  $Q_m \subseteq Q$  is the set of marked states. For convenience, we extend  $\delta$  to function  $\delta : Q \times \Sigma^* \to Q$  in the same way as we did in the untimed DES definition.

#### 2.3.1 Controllability and Supervision

Same as untimed DES, control for timed DES is described by disabling controllable events. The event set  $\Sigma$  is divided into controllable and uncontrollable events. We define the set of controllable events as  $\Sigma_c := \Sigma_{hib} \cup \{tick\}$  where  $\Sigma_{hib} \subseteq \Sigma_{act}$  is the set of activity events that can disabled by supervisors. Clearly, the difference between controllable events and prohibitable events is that the prohibitable events do not contain the *tick* event, as a *tick* event is disabled in the system to model the forcing of an event. We define the set of uncontrollable events for **G** as  $\Sigma_u := \Sigma - \Sigma_c$

Controllability for timed DES is defined as follows:

**Definition 2.2.** A language  $K \subseteq L(G)$  is said to be *controllable* with respect to G if,

$$(\forall s \in \overline{K})Elig_{\overline{K}}(s) \supseteq \begin{cases} Elig_{L(G)}(s) \cap (\Sigma_u \cup \{tick\}) & \text{if } Elig_{\overline{K}}(s) \cap \Sigma_{for} = \emptyset\\ Elig_{L(G)}(s) \cap \Sigma_u & \text{if } Elig_{\overline{K}}(s) \cap \Sigma_{for} \neq \emptyset \end{cases}$$

The above definition says tick can only be disabled when there exists an eligible forcible event to preempt the tick.

**Definition 2.3.** Supervisor  $\mathbf{S} = (X, \Sigma, \xi, x_0, X_m)$  is controllable with respect to  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  if for all  $s \in L(S) \cap L(G)$ ,

$$Elig_{L(S)}(s) \supseteq \begin{cases} Elig_{L(G)}(s) \cap (\Sigma_u \cup \{tick\}) & \text{if } Elig_{L(S)\cap L(G)}(s) \cap \Sigma_{for} = \emptyset \\ Elig_{L(G)}(s) \cap \Sigma_u & \text{if } Elig_{L(S)\cap L(G)}(s) \cap \Sigma_{for} \neq \emptyset \end{cases}$$

Note that the closed and marked behaviour of a TDES is defined in the same way as for an untimed DES. The definitions for nonblocking and language inclusion remains the same as for untimed DES.

## CHAPTER 3

## Sampled-Data Supervisory Control

In this chapter we present an overview of sampled-data supervisory control. Sampled-data supervisory control deals with the implementation of TDES supervisors as SD controllers. In order to translate a TDES supervisor to an SD controller such that it exhibits correct behaviour, we have to verify some additional properties about our system. The basic definitions and notations are presented briefly but not in detail. The details can be found in [Wan09, LW10]. We briefly introduce the sampled-data setting for TDES and the properties required to implement TDES systems as SD controllers. Here we are only concerned about effeciently verifying these properties. For details about how to convert a TDES supervisor to an SD controller, see [Wan09].

### 3.1 SD Controller

When using an SD controller to control a system, an input is associated with each event, and an output is associated with each controllable event. An event is considered to have occured when its corresponding input becomes true during a given clock period. A controllable event is considered to be enabled when its output is set to true by the controller, otherwise it is considered to be disabled. Finally, we associate the clock edge that drives the SD controller with the TDES *tick* event.

An SD controller samples the value of its inputs on each clock edge, and then

uses the information to decide what its next state is going to be. This means the SD controller only knows about its inputs at each clock edge, and all it knows is whether a given input is true or false. This only tells the controller that the event has occurred during the clock period that just ended. This means that an SD controller has no information about event ordering; i.e which event occurred first or last, as well as how many times the event occurred if it occurred more than once. The only ordering information that remains is which clock period did the event occur in. Also, an SD controller only changes state on a clock edge, meaning its outputs can only change at a clock edge, and then stay constant for the rest of the clock period. This means enablement and forcing decisions are determined right after the clock edge and cannot change until the next clock edge.

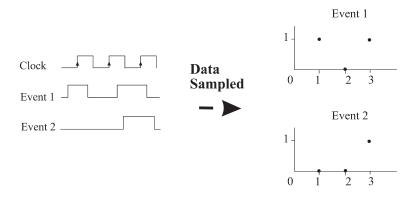

In Figure 3.1, we see on the third rising edge of the clock, the SD controller

Figure 3.1: Sampling Events

knows that both events e1 and e2 have occurred, but not which one occured first. This means that the SD controller cannot tell the difference between the strings *Event1-Event2-tick*, *Event2-Event1-tick*, or *Event1-Event2-Event1-tick*.

In TDES, the general assumptions are that events occur in a particular order, we know immediately when events occur and that there is no communication delay; i.e. enablement and forcing occurs immediately. These assumptions are not true in general for SD controllers, thus giving rise to concurrency and timing issues when implementing TDES as SD controllers. These issues bring up concerns with respect to controllability, nonblocking, plant model correctness, and the SD controller's ability to determine which state the TDES system currently is in. In [Wan09, LW10], the authors identify a number of existing TDES properties as well as introduce some new properties, in particular SD controllability, to address these issues and to make it easier to translate a TDES supervisor to an SD controller.

### 3.2 System Assumptions

To implement sampled-data controllers, the following assumptions are made about the system. It is up to the designer of the system to ensure that the system implements the following assumptions.

1) The set of prohibitable events is equal to the set of forcible events

$(\Sigma_{hib} = \Sigma_{for}).$

2) Enabling a forcible event means the event is forced to occur once in that clock period.

3) All SD controllers are implemented centrally with a common clock, such that all inputs are sampled at the same time and all outputs updated at the same time.

4) An event is assumed to have occured as soon as its input to the controller goes true. If the input goes true very close to a clock edge, it is assumed to occur immediately in the next sampling period.

5) When an event is forced to occur in a sampling period, it should occur only during that clock period and not the next one.

6) The length of an input signal should always be appropriate, so as to not be missed by SD controllers (too short) or not to be intrepreted to occur in multiple

clock periods (too long).

Applicable systems should not find Assumptions 1, 2, 5, and 6 very restrictive. Assumptions 3 and 4 partially address timing delay issues and are likely to be removed in future work.

### 3.3 SD Preliminaries

An SD controller can only observe  $\epsilon$  and strings ending with a *tick*. These strings are called *sampled strings* and are defined as:

$$L_{samp} = \Sigma^*.tick \cup \{\epsilon\}$$

where  $\Sigma$  is the system's event set.

*Concurrent strings* are all the strings possible in the system since the last sampled string and which end with a *tick* event. These strings determine the next state of an SD controller as the SD controller only changes state at each clock edge (the occurrence of *tick* event). They are defined as

$$L_{conc} = \Sigma_{act}^*.tick \subset L_{samp}$$

However, if two concurrent strings contain the same events but in different order and/or number, an SD controller would not be able to distinguish between the strings. To express this uncertainty we define the *occurrence operator*. The occurrence operator takes a string and returns the *occurrence image* of the string (the set of events that make up the string). For  $s \in \Sigma^*$ , the occurrence operator, Occu:  $\Sigma^* \to Pwr(\Sigma)$  is defined as:

$$Occu(s) = \{ \sigma \in \Sigma \mid s \in \Sigma^* \sigma \Sigma^* \}$$

For a TDES  $S = (X, \Sigma, \xi, x_0, X_m)$ , sampled states are those states that are reached by sampled strings; thus they are partially observable. They are defined as:

$$X_{samp} = \{ x \in X \mid (\exists s \in L(S) \cap L_{samp}) x = \xi(x_0, s) \}$$

Essentially, a controller starts at the initial state  $x_0$  and changes from one sampled state to the next as concurrent strings occur.

### 3.4 SD Properties

Described below are the conditions for TDES which are essential to implement sampled-data supervisory control.

#### **3.4.1** Plant Completeness

The concept of plant completeness was introduced by Balemi in [Bal94]. Balemi states that controllable events often are part of the supervisors implementation and can occur when we want them to occur. However, to make the system easier to model and understand, a plant can be modeled more restrictively.

**Definition 3.1.** A plant G is *complete* for for its supervisor S if

$$(\forall s \in L(G) \cap L(S))(\forall \sigma \in \Sigma_c) s \sigma \in L(S) \Longrightarrow s \sigma \in L(G)$$

The above definition is given in terms of controllable events which includes the *tick* event. As timed DES is just concerned with the occurrence of activity events, plant completeness has been adapted in [Wan09], to only apply to activity events and is defined below.

**Definition 3.2.** Let TDES G be a plant and TDES S be a supervisor. G is *complete* for S if

$$(\forall s \in L(G) \cap L(S))(\forall \sigma \in \Sigma_{hib}) s \sigma \in L(S) \Longrightarrow s \sigma \in L(G)$$

The above definition states that for every state in the plant  $\mathbf{G}$ , if a prohibitable event is enabled by the supervisor  $\mathbf{S}$ , it must be possible in the plant. If compared to the definition of a supervisor  $\mathbf{S}$  being controllable with respect to plant  $\mathbf{G}$ , we can see that it's the same if we switch the supervisor  $\mathbf{S}$  with plant  $\mathbf{G}$  and replace controllable events with uncontrollable events.

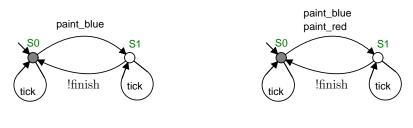

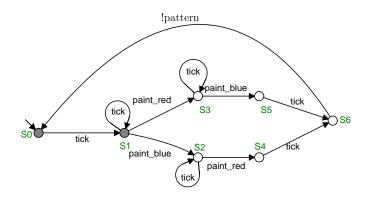

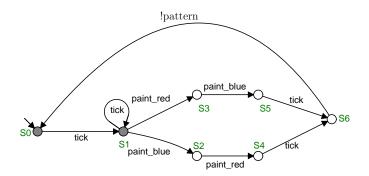

Figure 3.2: Plant

Figure 3.3: Supervisor

Figure 3.2 and 3.3 show a plant and a supervisor in which the plant is not complete for the supervisor. At state **S0** in the plant, event *paint\_red* is not eligible, while its eligible at state **S0** in the supervisor.

#### 3.4.2 Activity Loop Free

To ensure that a TDES does not allow a *tick* event to be indefinitely preempted by activity events, it is required that the TDES be activity loop free (ALF) [BW94]. In a TDES, activity events ( $\Sigma_{act} \subseteq \Sigma$ ) are non-tick events which show a sequence of events occuring over a period of time. The occurence of a *tick* event represents the notion of time passing, allowing us to specify time bounds for the occurence of activity events. Therefore, it is desired that the sequence of activity events terminate after a finite number of steps, ensuring that our TDES does not model the unrealistic situation where an activity event loop could be executed continuously by indefinitely preempting a *tick* event. **Definition 3.3.** A TDES  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  is activity loop free if

$$(\forall q \in Q_{reach})(\forall s \in \Sigma_{act}^+)\delta(q, s) \neq q$$

where  $Q_{reach} \subseteq Q$  is the set of all reachable states of **G**.

The plant in Figure 3.2 fails the ALF condition since at state **S1**, the loop  $paint\_blue - finish$  can occur an infinite number of times with no *tick* event.

The ALF condition is only applied to the system's closed-loop behaviour. The supervisors are not required to be ALF as they may contain self-loops that are not possible in the plant. However, selfloops essentially provide enablement information but do not have any useful next-state information for SD controllers, so they can be ignored for translation purposes. The definition given below makes supervisors much easier to translate. It states that if selfloops of any activity events are removed from the TDES, the rest of the TDES must be ALF.

**Definition 3.4.** Let  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$  be a TDES, and let G' be  $\mathbf{G}$  with all activity event selfloops removed.  $\mathbf{G}$  is non-selfloop activity loop free if G' is ALF.

The proposition below states that if individual DES are all ALF, then the synchronous product of these DES is also ALF. This means that we can simply check the individual DES to check whether the system is ALF instead of checking the whole system at once.

**Proposition 3.1.** [Wan09] For TDES  $G_1$  and  $G_2$ , if  $G_1$  and  $G_2$  are each ALF then their synchronous product  $\mathbf{G} = G_1 \parallel G_2$  is ALF.

#### 3.4.3 Proper Time Behaviour

To make sure that the closed-loop system would not reach a state at which no more *tick* events are ever possible, it is required for the plant to have proper time behaviour, as defined by Kai Wong et. al. [WW96].

**Definition 3.5.** TDES G has a proper time behaviour if

$$(\forall q \in Q_{reach}) (\exists \sigma \in \Sigma_u \cup tick) \delta(q, \sigma)!$$

The above definition says that at every reachable state of the system, either an uncontrollable event or a *tick* event must be possible. This condition ensures that when a controllable event is disabled by a supervisor, there is either a *tick* event or an uncontrollable event still possible. This condition is applied only to the plant TDES.

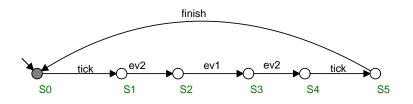

Figure 3.4: Example TDES for SD Properties

The TDES in Figure 3.4 fails proper time behaviour since at state S5 only a prohibitable event *finish* is eligible which could be disabled by the supervisor effectively "stopping the clock".

#### 3.4.4 S-singular Prohibitable Behaviour

Another restriction on our system is S-singular prohibitable behaviour, where TDES S is the supervisor. This property reflects the fact that SD controllers only allow prohibitable events to occur once during a sampling period. This requirement make sure the plant models this correctly, instead of showing behavior that will never physically occur. We define this property as: **Definition 3.6.** For TDES  $G = (Q, \Sigma, \delta, q_0, Q_m)$  and TDES  $S = (X, \Sigma, \xi, x_0, X_m)$ , G has S-singular prohibitable behaviour if  $(\forall s \in L(S) \cap L(G) \cap L_{samp})(\forall s \in \Sigma^*_{act})ss' \in L(S) \cap L(G) \Longrightarrow$  $(\forall \sigma \in Occu(s') \cap \Sigma_{hib})\sigma \notin Elig_{L(G)}(ss')$

The TDES **G** in Figure 3.4 fails S-singular prohibitable behaviour as the prohibitable event ev2 occurs twice in a sampling period.

#### 3.4.5 SD Controllable Languages

The conditions that a TDES closed-loop system has finite statespace, be ALF and nonblocking, that the plant have proper time behaviour and be complete for the supervisor, and that the supervisor be controllable for the plant does not guarantee that the system behaviour under the control of the SD controllers would be nonblocking and controllable. Therefore another property called SD controllability is introduced to address these concerns and is defined as:

**Definition 3.7.** A supervisor  $S = (X, \Sigma, \xi, x_0, X_m)$  is said to be *SD controllable* with respect to  $G = (Q, \Sigma, \delta, q_0, Q_m)$  if,  $\forall s \in L(S) \cap L(G)$ , the following statements are satisfied:

- i)  $Elig_{L(G)}(s) \cap \Sigma_u \subseteq Elig_{L(S)}(s)$

- ii) If  $tick \in Elig_{L(G)}(s)$  then

tick

$$\in Elig_{L(S)}(s) \Leftrightarrow Elig_{L(S)\cap L(G)}(s) \cap \Sigma_{hib} = \emptyset$$

iii) If  $s \in L_{samp}$  then

1.

$$(\forall s \in \Sigma_{act}^*)[ss' \in L(S) \cap L(G)] \Longrightarrow$$

$[Elig_{L(S)\cap L(G)}(ss') \cup Occu(s')] \cap \Sigma_{hib} = Elig_{L(S)\cap L(G)}(s) \cap \Sigma_{hib}$

2.  $(\forall s', s'' \in L_{conc})[ss', ss'' \in L(S) \cap L(G) \wedge Occu(s') = Occu(s'')] \Rightarrow$

$ss' \equiv_{L(S)\cap L(G)} ss'' \wedge ss' \equiv_{L_m(S)\cap L_m(G)} ss''$

iv)  $L_m(S) \cap L_m(G) \subseteq L_{samp}$

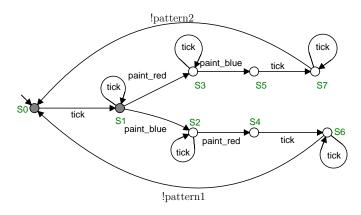

Figure 3.5: SD Controllability Example 1 - Plant

Figure 3.6: SD Controllability Example 1 - Supervisor

Point (i) in this definition is the standard untimed controllability condition. Combined with point ii ( $\Leftarrow$ ) part it implies standard timed DES controllability. Point ii ( $\Rightarrow$ ) part states that we must disable a *tick* event if we enable a prohibitable event that is possible in the plant. Point (iii.1) states that if an event is possible in a clock period, it must be possible immediately after the *tick* and stay possible in the clock period until it occurs. Point (iii.2) says all concurrent strings with the same occurrence image in a clock period must have the same future with respect to the closed and marked behaviour of the system. Point (iv) says all marked strings must be sampled strings. Combined with point (iii.2) this ensures that if our TDES system is nonblocking then our plant and SD controller will be nonblocking as well.

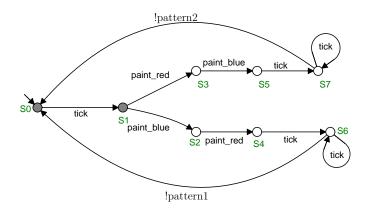

Figure 3.7: SD Controllability Example 2 - Plant

Figure 3.8: SD Controllability Example 2 - Supervisor

#### 3.4.5.1 SD Controllability Examples

Figures 3.5 and 3.6 show a plant and supervisor such that the plant and supervisor satisfy SD controllability point(i), point(ii) and point(iii.1), but fails to satisfy point (iii.2) and (iv). In the system, state **S1**, which is a sampled state, leads to states **S6** and **S7** by concurrent strings with the same occurrence image  $\{paint\_blue, paint\_red, tick\}$ .

According to point(iii.2), the states S6 and S7 should represent the same

nerode equivalent cells of the system with respect to its closed and marked behaviour. But state **S6** leads to state **S0** by *pattern1* event, while state **S7** leads to state **S0** by *pattern2* event. Clearly the states do not have the same future with respect to the closed behaviour of the system.

Also, event *pattern1* and *pattern2* lead to State S0 which is a marked state. This violates point(iv) of SD controllability definition as point(iv) requires all marked strings to be sampled strings; thus only the *tick* event should lead us to a marked state.

In Figure 3.7 and 3.8, we show a modified version of the the system from Figure 3.5 and 3.6. In this example, the system fails to satisfy point (ii), but satisfies the point(iii.2) of SD controllability definition. At state S1, the event *tick* and the prohibitable events *paint\_blue*, and *paint\_red* are eligible. According to point(ii), *tick* should be disabled by the supervisor if there is a prohibitable event eligible to preempt *tick*.

# CHAPTER 4

# **Compositional Verification for SD Properties**

In this thesis, we present new definitions for the sampled data supervisory control properties. These new representations express the required properties for sampled-data supervisory control in terms of other properties such as controllability, nonblocking or language inclusion. This makes it easy to see exactly what checks need to be performed for compositional verification, and on which components. These properties already have existing compositional methods defined for them, so the methods can be reused.

We have organised the compositional verification of the properties required for sampled-data supervisory control into two separate chapters for better readability. In this chapter, we discuss the properties plant completeness, activity loop free, S-singular prohibitable behaviour and proper time behaviour. The next chapter focuses on SD controllability. We will show that these new representations are equivalent to the definitions of the properties that we presented in Section 3.4.

### 4.1 Plant Completeness

We now restate the plant completeness property (see page 19) in terms of standard untimed controllability. We can state the untimed controllability definition from Section 2.2.3 in the alternate form below:

**Definition 4.1.** Let TDES G =  $(Q, \Sigma, \delta, q_0, Q_m)$  be a plant and TDES S =

$(X, \Sigma, \xi, x_0, X_m)$  be a supervisor. S is said to be controllable with respect to G if

$$(\forall s \in L(S))(\forall \sigma \in \Sigma_u) s \sigma \in L(G) \Longrightarrow s \sigma \in L(S)$$

Comparing the plant completeness definition to the above definition, we can easily see that we can adapt the controllability check by relabelling plants as supervisors, supervisors as plants, prohibitable events as uncontrollable events, and uncontrollable events as controllable events. After relabelling, we can just apply the compositional verification algorithm for standard controllability [BMM04] on the relabelled system.

### 4.2 Activity Loop Free

In this section, we develop a method to verify if a TDES  $\mathbf{G}$  is Activity-loop free (ALF) (see definition on page 20). To do this we will use the concept of paths.

Let  $\mathbf{G} = (Q, \Sigma, \delta, q_0, Q_m)$ . A path in  $\mathbf{G}$  is an alternating sequence of states and events

$$\pi = q_0 \xrightarrow{\sigma_1} \dots \xrightarrow{\sigma_n} q_n$$

where  $\delta(q_i, \sigma_{i+1}) = q_{i+1}$  for all  $0 \le i \le n$ . State  $q_0$  is called its origin and state  $q_n$  its end.  $L(\pi) = \sigma_1 \dots \sigma_n$  is the label of path  $\pi$ . The language accepted by the TDES G is

$L(G) = \{ L(\pi) \mid \pi \text{ is a path in } G \text{ with } q_0 \text{ as origin } \}.$

**Definition 4.2.** For TDES  $G = (Q, \Sigma, \delta, q_0, Q_m)$  and  $\Sigma_{act} \subseteq \Sigma$ , a path  $\pi$  in G is called a  $\Sigma_{act}$ -path if  $L(\pi) \in \Sigma_{act}^*$ . A  $\Sigma_{act}$ -loop is a  $\Sigma_{act}$ -path of length (i.e.  $|L(\pi)|$ ) at least one with the same origin and end. A  $\Sigma_{act}$ -loop is reachable in G if its origin is reachable in G. If G does not contain any reachable  $\Sigma_{act}$ -loops, G is called  $\Sigma_{act}$ -loop free.

For two TDES defined over the same alphabet set, it is sufficient to show that only one of the TDES is  $\Sigma_{act}$ -loop free, to show that the whole system is  $\Sigma_{act}$ -loop free [MM06].

The Lemma below shows that we can use the existing modular loop-detecting algorithm [MM06] to determine if **G** is ALF.

**Lemma 4.1.** *G* is activity loop free iff G is  $\Sigma_{act}$ -loop free.

*Proof.* This is obvious from the ALF definition and the  $\Sigma_{act}$ -loop free definition.

### 4.3 S-singular Prohibitable Behaviour

The S-singular prohibitable behaviour property (see page 22) requires that a prohibitable event be allowed to occur in the plant only once during a sampling period. We can state the definition in the alternative form below:

**Definition 4.3.** Let TDES  $G = (Y, \Sigma, \delta, y_0, Y_m)$  and TDES  $S = (X, \Sigma, \xi, x_0, X_m)$ . G has S-singular prohibitable behaviour if  $(\forall s \in L(G) \cap L(S) \cap L_{samp})(\forall t \in \Sigma_{act}^*)(\forall \sigma \in \Sigma_{hib})$  $(st \in L(S) \cap L(G)) \land (st \sigma \in L(G)) \Rightarrow \sigma \notin Occu(t)$

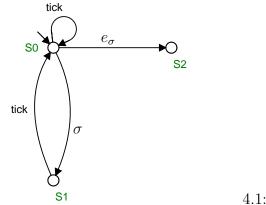

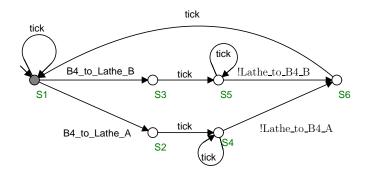

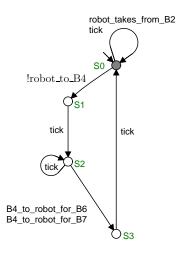

4.1: TDES  $T^{\sigma}$

**Definition 4.4.** Let  $G = (X, \Sigma, \delta, x_0, X_m), \sigma \in \Sigma_{hib}, e_\sigma \notin \Sigma, E_\sigma = \{\sigma, e_\sigma, tick\}.$ Let  $P_{E_\sigma} : \Sigma^* \to E_\sigma^*$  be a natural projection. Construct TDES  $G^\sigma$  such that  $L(G^\sigma) = L(G) \cup \{se_\sigma \mid s\sigma \in L(G)\}.$

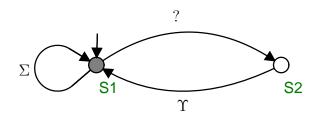

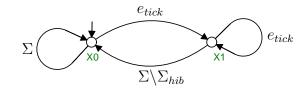

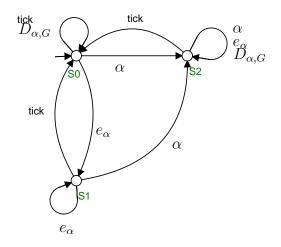

We express this property as a language inclusion problem by introducing, for each  $\sigma \in \Sigma_{hib}$ , a new DES  $T^{\sigma}$  which exhibits the behaviour that the event  $\sigma$  can only occur once between tick events. We then construct  $T^{\sigma} = (X_T, \Sigma_T, \delta_T, x_0, X_{T_m})$  as shown in Figure 4.1.

We now present two lemmas related to  $T^{\sigma}$  that will be useful later, in this section.

# Lemma 4.2. $L(T^{\sigma}) = \overline{(\{\epsilon, \sigma\} tick)^* e_{\sigma}}$

*Proof.* It is sufficient to show: I)  $L(T^{\sigma}) \supseteq \overline{(\{\epsilon, \sigma\} tick)^* e_{\sigma}}$  and II)  $L(T^{\sigma}) \subseteq \overline{(\{\epsilon, \sigma\} tick)^* e_{\sigma}}$ Part I) Show:  $L(T^{\sigma}) \supseteq \overline{(\{\epsilon, \sigma\} tick)^* e_{\sigma}}$ Let  $s \in \overline{(\{\epsilon, \sigma\} tick)^* e_{\sigma}}$ We will show that  $s \in L(T^{\sigma})$ Having  $s \in \overline{(\{\epsilon,\sigma\}tick)^*e_{\sigma}}$  implies that there exists  $s' \in E_{\sigma}^*$  such that  $ss' \in C_{\sigma}^*$  $(\{\epsilon, \sigma\} tick)^* e_{\sigma}.$ Let s'' = ss'Since  $s'' \in (\{\epsilon, \sigma\} tick)^* e_{\sigma}$ , there exists  $t \in (\{\epsilon, \sigma\} tick)^*$  such that  $s'' = te_{\sigma}$ . We note that  $\{\epsilon, \sigma\}$  tick =  $\{tick, \sigma tick\}$ . From Figure 4.1, we see that  $\delta_T(S0, tick) = S0$ Also  $\delta_T(S0, \sigma) = S1$  and  $\delta_T(S1, tick) = S0$ . This implies  $\delta_T(S0, t') = S0$  for all  $t' \in \{\epsilon, \sigma\} tick$ . (1)Now we will show that for all  $t \in (\{\epsilon, \sigma\} tick)^*$  it holds that  $\delta_T(S0, t) = S0$ . Since  $t \in (\{\epsilon, \sigma\} tick)^*$  there exists  $n \in N_0$  such that  $t \in (\{\epsilon, \sigma\} tick)^n$ We will show by induction on n that  $\delta_T(S0, t) = S0$ Inductive Base: n = 0

$\mathbf{t} \in (\{\epsilon, \sigma\} tick)^0 \Rightarrow \mathbf{t} = \epsilon$

Clearly  $\delta_T(S0, \epsilon) = S0.$

Inductive Step:  $n \to n+1$ ,  $t \in (\{\epsilon, \sigma\} tick)^{n+1}$

By inductive assumption,  $\delta_T(S0, t) = S0$  for  $t \in (\{\epsilon, \sigma\} tick)^n$ .

$t' \in (\{\epsilon, \sigma\} tick)^{n+1} \Rightarrow t' \in (\{\epsilon, \sigma\} tick)^n \{\epsilon, \sigma\} tick$

By (1) we have  $\delta_T(S0, t'') = S0$  for all  $t'' \in \{\epsilon, \sigma\}$  tick and by inductive assumption we have  $\delta_T(S0, t) = S0$  for  $t \in (\{\epsilon, \sigma\}$  tick)<sup>n</sup>.

This implies that  $\delta_T(S0, t') = S0$  for  $t' \in (\{\epsilon, \sigma\} tick)^{n+1}$ .

Inductive step complete.

We thus conclude that for  $t \in (\{\epsilon, \sigma\} tick)^*$  it holds that  $\delta_T(S0, t) = S0$

We have  $s'' = te_{\sigma}$

Clearly from the Figure 4.1,  $\delta_T(S0, e_{\sigma}) = S2$ .

$$\implies s'' \in L(T^{\sigma})$$

Since  $L(T^{\sigma})$  is a prefix closed language and  $s \leq s''$ , we have  $s \in L(T^{\sigma})$  as required. Part I complete.

Part II) Show:  $L(T^{\sigma}) \subseteq \overline{(\{\epsilon, \sigma\} tick)^* e_{\sigma}}$

Let  $s \in L(T^{\sigma})$ .

We now show that  $s \in \overline{(\{\epsilon, \sigma\} tick)^* e_{\sigma}}$ .

Since  $s \in L(T^{\sigma})$  this implies  $\delta_T(S0, s) = X$  for some  $X \in \{S0, S1, S2\}$ .

We will first examine case X = S0 and X = S1.

Clearly from Figure 4.1, X = S0 or X = S1 implies s does not contain  $e_{\sigma}$ .

First we will show by induction on |s| that:

- 1) If  $\delta_T(S0, s) = S0$  then  $s \in (\{\epsilon, \sigma\} tick)^*$  and

- 2) if  $\delta_T(S0, s) = S1$  then  $s \in (\{\epsilon, \sigma\} tick)^* \sigma$

Inductive Base:  $n = 0, s = \epsilon$

Clearly  $\epsilon \in (\{\epsilon, \sigma\} tick)^*$  and  $\delta_T(S0, \epsilon) = S0$ .

**Inductive Step:**  $n \to n+1$ ,  $s = t\alpha$  with  $\alpha \in \{\sigma, tick\}$

By inductive assumption:

1) If  $\delta_T(S0, t) = S0$  then  $t \in (\{\epsilon, \sigma\} tick)^*$  and

2) If  $\delta_T(S0, t) = S1$  then  $t \in (\{\epsilon, \sigma\} tick)^* \sigma$

Since  $s \in L(T^{\sigma})$  there exists state y such that  $\delta_T(S0, t) = y$  and  $\delta_T(y, \alpha) = X$ .

Clearly from the Figure 4.1, y is either S0 or S1.

Case (X = S0)

Clearly from Figure 4.1, only a tick transition allows  $\delta_T(y, \alpha) = S0$ , thus  $\alpha = tick$ . case i) if (y = S0) $\implies \delta_T(S0, t) = S0$ By inductive assumption,  $t \in (\{\epsilon, \sigma\} tick)^*$  $\implies s = t\alpha \in (\{\epsilon, \sigma\} tick)^* tick$  $\implies s \in (\{\epsilon, \sigma\} tick)^*$ case ii) if (y = S1) $\implies \delta_T(S0, t) = S1$ By inductive assumption, t  $\in (\{\epsilon, \sigma\}tick)^*\sigma$  $\implies s = t\alpha \in (\{\epsilon, \sigma\} tick)^* \sigma tick$  $\implies s \in (\{\epsilon, \sigma\} tick)^*$ By case i) and ii) we can conclude that if  $\delta_T(S0, s) = S0$  then  $s \in (\{\epsilon, \sigma\} tick)^*$ (2)Case (X = S1)Clearly from Figure 4.1, only a  $\sigma$  transition allows  $\delta_T(y, \alpha) = S1$  only from the state S0.

$\Rightarrow \alpha = \sigma \text{ and } y = S0$  $\Rightarrow \delta_T(S0, t) = S0$ By inductive assumption,  $t \in (\{\epsilon, \sigma\} tick)^*$  since  $\delta_T(S0, \sigma) = S1$  $\Rightarrow s = t\alpha \in (\{\epsilon, \sigma\} tick)^* \sigma$  $\Rightarrow s \in (\{\epsilon, \sigma\} tick)^* \sigma \text{ as required.}$  Inductive step complete.

We have now shown that:

(a) for X = S0, s

$$\in (\{\epsilon, \sigma\}tick)^* \subseteq \overline{(\{\epsilon, \sigma\}tick)^*e_{\sigma}}$$

(b) for X = S1, s  $\in (\{\epsilon, \sigma\}tick)^*\sigma \subseteq \overline{(\{\epsilon, \sigma\}tick)^*e_{\sigma}}$

Now we examine the case  $\delta_T(S0, s) = S2$

(3)

Clearly from Figure 4.1,  $\delta_T(S0, e_{\sigma}) = S2$  and this is the only way to get to S2.  $\Rightarrow (\exists t) \ s = te_{\sigma} \ and \ \delta_T(S0, t) = S0.$ By (3), this implies  $t \in (\{\epsilon, \sigma\}tick)^*$   $\Rightarrow s = te_{\sigma} \in (\{\epsilon, \sigma\}tick)^*e_{\sigma} \subseteq \overline{(\{\epsilon, \sigma\}tick)^*e_{\sigma}}$ Now we have shown for all  $X \in \{S0, S1, S2\}$ ,  $s \in \overline{(\{\epsilon, \sigma\}tick)^*e_{\sigma}}$ Part II complete. Thus we can conclude that  $L(T^{\sigma}) = \overline{(\{\epsilon, \sigma\}tick)^*e_{\sigma}}$

**Lemma 4.3.** Let  $\sigma \in \Sigma$  and  $E_{\sigma} = \{\sigma, e_{\sigma}, tick\}$ . Then  $s \in \overline{(\{\epsilon, \sigma\}tick)^*}$  iff  $s \in (\{\epsilon, \sigma\}tick)^n \{\epsilon, \sigma\}$  for some  $n \in N_0 = \{0, 1, 2, 3, \dots\}$

*Proof.* To show our claim, we have to show:

I)

$$s \in \overline{(\{\epsilon, \sigma\}tick)^*} \Longrightarrow s \in (\{\epsilon, \sigma\}tick)^n \{\epsilon, \sigma\}$$

for some  $n \in N_0$  and

II)  $s \in (\{\epsilon, \sigma\}tick)^n \{\epsilon, \sigma\}$  for some  $n \in N_0 \Longrightarrow s \in \overline{(\{\epsilon, \sigma\}tick)^*}$

Part I) Show:  $s \in \overline{(\{\epsilon, \sigma\}tick)^*} \Longrightarrow s \in (\{\epsilon, \sigma\}tick)^n \{\epsilon, \sigma\}$  for some  $n \in N_0$ .

Let  $s \in \overline{(\{\epsilon, \sigma\}tick)^*}$ .

This implies there exists  $s' \in E^*_{\sigma}$  such that  $ss' \in (\{\epsilon, \sigma\} tick)^*$ .

This implies there exists some  $n \in N_0$  such that  $ss' \in (\{\epsilon, \sigma\} tick)^n$ .

Appending  $\{\epsilon, \sigma\}$  to both sides we get

$ss'\{\epsilon,\sigma\} \in (\{\epsilon,\sigma\}tick)^n\{\epsilon,\sigma\}$  from some  $n \in N_0$ .

Since  $s \leq ss'\{\epsilon, \sigma\} \in (\{\epsilon, \sigma\}tick)^n\{\epsilon, \sigma\}$  from some  $n \in N_0$ .

Clearly by taking  $n' \leq n$ , we can use  $(\{\epsilon, \sigma\} tick)^{n'} \{\epsilon, \sigma\}$  to contain any prefix of  $ss'\{\epsilon, \sigma\}$ .

This implies  $s \in (\{\epsilon, \sigma\} tick)^n \{\epsilon, \sigma\}$  from some  $n \in N_0$  as required.

Part I complete.

Part II) Show:  $s \in (\{\epsilon, \sigma\} tick)^n \{\epsilon, \sigma\}$  for some  $n \in N_0 \Longrightarrow s \in \overline{(\{\epsilon, \sigma\} tick)^*}$ . Let  $s \in (\{\epsilon, \sigma\} tick)^n \{\epsilon, \sigma\}$  for some  $n \in N_0$ .

Appending tick to both sides, we get:

s tick  $\in (\{\epsilon, \sigma\} tick)^n \{\epsilon, \sigma\} tick$  for some  $n \in N_0$ .  $\implies$  s tick  $\in (\{\epsilon, \sigma\} tick)^{n+1}$  for some  $n \in N_0$ .  $\implies$  s tick  $\in (\{\epsilon, \sigma\} tick)^*$ .  $\implies$  s  $\in \overline{(\{\epsilon, \sigma\} tick)^*}$ , as required. Part II complete.

By part I and II we conclude that  $s \in \overline{(\{\epsilon, \sigma\}tick)^*}$  iff  $s \in (\{\epsilon, \sigma\}tick)^n \{\epsilon, \sigma\}$  for some  $n \in N_0 = \{0, 1, 2, 3, \dots\}$ .

We will prove that our language inclusion property is equivalent to the S-singular prohibitable behaviour property. The proof that follows is based on an initial proof sketch by the author's thesis supervisors, Dr. R. Malik and Dr. R. Leduc.

**Theorem 4.1.** Let TDES  $G = (X, \Sigma, \delta, x_0, X_m)$  and  $S = (Y, \Sigma, \xi, y_0, Y_m)$ . G has S-singular prohibitable behaviour iff  $(\forall \sigma \in \Sigma_{hib}) P_{E_{\sigma}}(L(G^{\sigma} \parallel S)) \subseteq L(T^{\sigma})$

*Proof.* To prove this claim, we will need to show

I) G has S-singular prohibitable behaviour

$\Rightarrow (\forall \sigma \in \Sigma_{hib}) P_{E_{\sigma}}(L(G^{\sigma} \parallel S)) \subseteq L(T^{\sigma}).$

II)  $(\forall \sigma \in \Sigma_{hib}) P_{E_{\sigma}}(L(G^{\sigma} \parallel S)) \subseteq L(T^{\sigma})$

$\Rightarrow$  G has S-singular prohibitable behaviour.

Part I) Show G has S-singular prohibitable behaviour  $\implies$

$$(\forall \sigma \in \Sigma_{hib}) P_{E_{\sigma}}(L(G^{\sigma} \parallel S)) \subseteq L(T^{\sigma})$$

Assume G has S-singular prohibitable behaviour.

Let

$$\sigma \in \Sigma_{hib}, s \in L(G^{\sigma} \parallel S)$$

(1)

We show by induction on n = |s| that  $P_{E_{\sigma}}(s) \in L(T^{\sigma})$ .

Sufficient to show that  $P_{E_{\sigma}}(s) \in \overline{(\{\epsilon, \sigma\} tick)^* e_{\sigma}}$  by Lemma 4.2

Inductive Base:  $n = 0, s = \epsilon$

Then

$$P_{E_{\sigma}}(s) = P_{E_{\sigma}}(\epsilon) = \epsilon \in (\{\epsilon, \sigma\} tick)^* e_{\sigma}$$

Inductive Step:  $n \rightarrow n+1, s = t\alpha$

By inductive assumption,  $P_{E_{\sigma}}(t) \in \overline{(\{\epsilon, \sigma\} tick)^* e_{\sigma}}$

We know by (1) that

$$t\alpha = s \in L(G^{\sigma}) = L(G) \cup \{se_{\sigma} \mid s\sigma \in L(G)\}.$$

That means if s contains  $e_{\sigma}$ , then  $e_{\sigma}$  is only the last event of s.

That is  $e_{\sigma} \notin Occu(t)$ , and  $t \in \Sigma^*$ .

Therefore

$$P_{E_{\sigma}}(t) \in \overline{(\{\epsilon, \sigma\} tick)^*}$$

and  $t \in L(G)$  (by construction of  $G^{\sigma}$ ). (2)

Also,

$$t \le s \in L(G^{\sigma} \parallel S)$$

and  $t \in \Sigma^* \Rightarrow t \in L(G) \cap L(S)$ . (3)

Consider four cases:

a)  $\alpha \notin \{\sigma, e_{\sigma}, tick\}$

Then  $P_{E_{\sigma}}(s) = P_{E_{\sigma}}(t\alpha) = P_{E_{\sigma}}(t) \in \overline{(\{\epsilon, \sigma\}tick)^*e_{\sigma}}$  by inductive assumption. b)  $\alpha = tick$

Then since  $P_{E_{\sigma}}(t) \in \overline{(\{\epsilon, \sigma\} tick)^*}$  by (2) we have:

$$P_{E_{\sigma}}(t) \in (\{\epsilon, \sigma\} tick)^n \{\epsilon, \sigma\}$$

for some  $n \in N_0$ , by Lemma 4.3.

Thus,  $P_{E_{\sigma}}(s) = P_{E_{\sigma}}$  (t tick) =  $P_{E_{\sigma}}(t)tick$  implies that:

$$P_{E_{\sigma}}(s) \in (\{\epsilon, \sigma\} tick)^n \{\epsilon, \sigma\} tick$$

$$\Rightarrow P_{E_{\sigma}}(s) \in (\{\epsilon, \sigma\} tick)^{n+1}$$

$$\Rightarrow P_{E_{\sigma}}(s) \in (\{\epsilon, \sigma\} tick)^*$$

Appending  $e_{\sigma}$  to this string gives:  $P_{E_{\sigma}}(s)e_{\sigma} \in (\{\epsilon, \sigma\}tick)^*e_{\sigma}$

We thus have:

$$P_{E_{\sigma}}(s) \in (\{\epsilon, \sigma\} tick)^* e_{\sigma}$$

c)

$$\alpha = \sigma$$

Let t =uv such that  $u \in L_{samp}$  and  $v \in \Sigma_{act}^*$ . We thus have:

$P_{E_{\sigma}}(u) \leq P_{E_{\sigma}}(uv) = P_{E_{\sigma}}(t) \in \overline{(\{\epsilon, \sigma\} tick)^*}$  $\implies P_{E_{\sigma}}(u) \in \overline{(\{\epsilon, \sigma\} tick)^*}$  $\implies P_{E_{\sigma}}(u) \in (\{\epsilon, \sigma\} tick)^n \{\epsilon, \sigma\} \text{ for some } n \in N_0 \text{ by Lemma 4.3}$ Since  $u \in L_{samp}$ ,  $P_{E_{\sigma}}(u)$  cannot end with  $\sigma$ . We thus have:

$$P_{E_{\sigma}}(u) \in (\{\epsilon, \sigma\} tick)^n \subseteq (\{\epsilon, \sigma\} tick)^*.$$

From (3), it follows that  $uv = t \in L(G) \cap L(S)$  and that:

$$u \leq t \Longrightarrow u \in L(G) \cap L(S) \cap L_{samp}.$$

Also  $s = t\sigma \in L(G^{\sigma}) = L(G) \cup \{we_{\sigma} \mid w\sigma \in L(G)\}$  with  $\sigma \neq e_{\sigma}$

$\Rightarrow uv\sigma = s \in L(G).$

Then, given that  $\sigma \in \Sigma_{hib}$ , it follows from the definition of S-singular prohibitable behaviour that  $\sigma \notin Occu(v)$ .

$$\implies P_{E_{\sigma}}(v) = \epsilon \text{ since } v \in \Sigma_{act}^*.$$

Thus,  $P_{E_{\sigma}}(t) = P_{E_{\sigma}}(uv) = P_{E_{\sigma}}(u) \in (\{\epsilon, \sigma\} tick)^*.$

Appending  $\sigma ticke_{\sigma}$  to this string gives:

$P_{E_{\sigma}}(s)ticke_{\sigma} = P_{E_{\sigma}}(t\sigma)ticke_{\sigma} = P_{E_{\sigma}}(t)\sigma ticke_{\sigma}$   $\Rightarrow P_{E_{\sigma}}(s)ticke_{\sigma} \in (\{\epsilon, \sigma\}tick)^{*}\sigma ticke_{\sigma}$   $\Rightarrow P_{E_{\sigma}}(s)ticke_{\sigma} \in (\{\epsilon, \sigma\}tick)^{*}e_{\sigma}$ We thus have:  $P_{E_{\sigma}}(s) \in \overline{(\{\epsilon, \sigma\}tick)^{*}e_{\sigma}}$ d)  $\alpha = e_{\sigma}$ Let t = uv such that  $u \in L_{samp}$  and  $v \in \Sigma_{act}^{*}$ .

Since  $P_{E_{\sigma}}(u) \leq P_{E_{\sigma}}(uv) = P_{E_{\sigma}}(t) \in \overline{(\{\epsilon, \sigma\}tick)^{*}}$ , we have:  $P_{E_{\sigma}}(u) \in \overline{(\{\epsilon, \sigma\}tick)^{*}}$   $\Rightarrow P_{E_{\sigma}}(u) \in (\{\epsilon, \sigma\}tick)^{*} \{\epsilon, \sigma\} \text{ for some } n \in N_{0} \text{ by Lemma 4.3.}$ Since  $u \in L_{samp}$ ,  $P_{E_{\sigma}}(u)$  cannot end with  $\sigma$ . This implies: